Dans le cadre de l’IEDM, l’entreprise a fixé le cap de ses recherches pour les prochaines années. Au programme : des “Quasi-Monolithic Chips” ou encore des transistors avec un matériau de canal 2D de 3 atomes d’épaisseur.

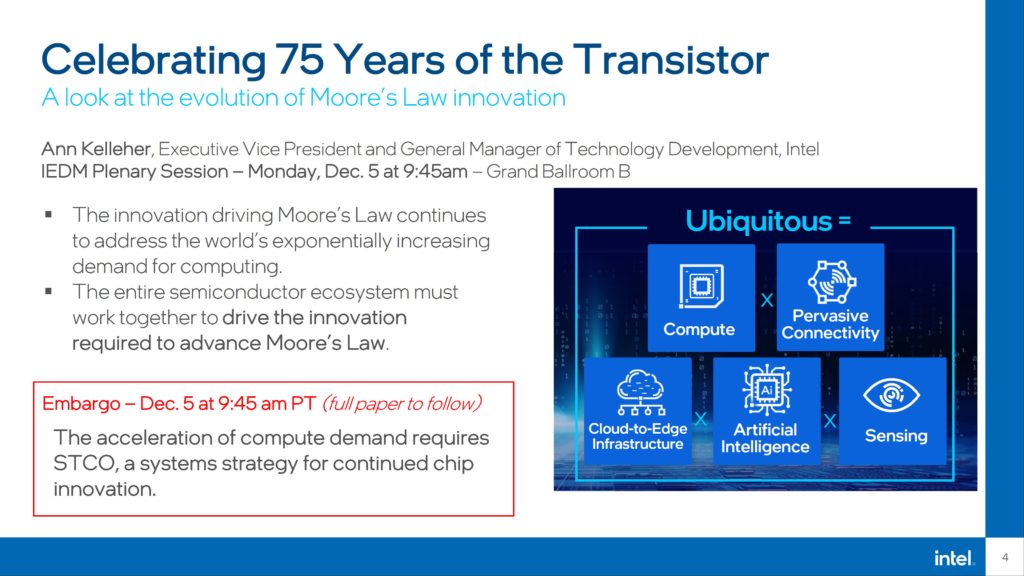

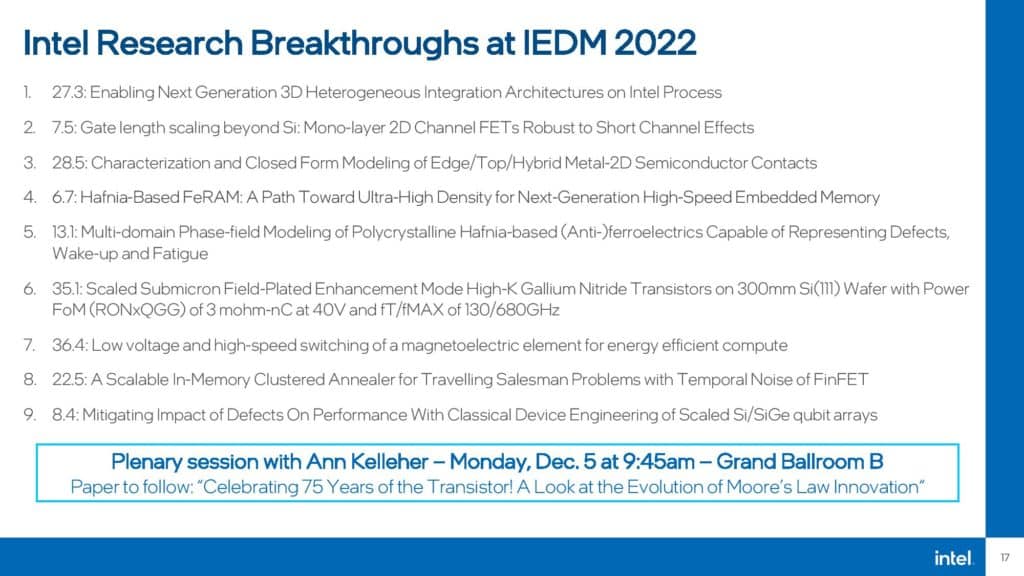

À l’occasion de l’IEDM (International Electron Devices Meeting) 2022, Intel a publié plusieurs documents qui jettent les bases des futures conceptions de puces de l’entreprise, à l’horizon 2030. Les chercheurs ont ainsi présenté une nouvelle technologie d’encapsulation 3D susceptible de multiplier par 10 la densité ; de nouveaux transistors qui iront au-delà des transistors RibbonFET avec un matériau de canal 2D de seulement 3 atomes d’épaisseur.

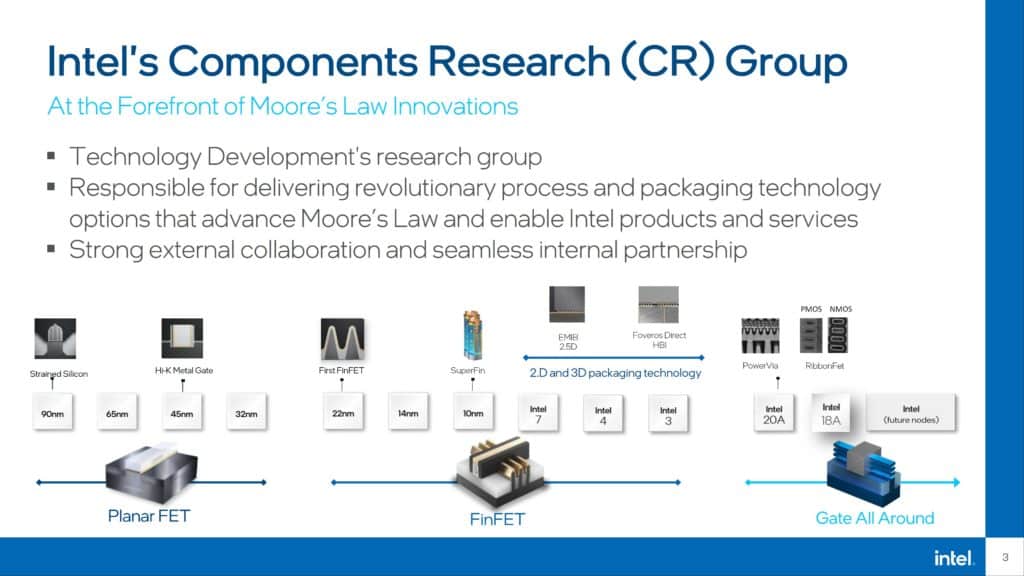

Le groupe de recherche sur les composants d’Intel cible trois domaines clés pour poursuivre l’évolution de la loi de Moore : une nouvelle technologie de conditionnement par collage hybride 3D pour permettre l’intégration transparente des puces ; des matériaux 2D ultraminces pour faire tenir plus de transistors sur une seule puce ; et de nouvelles possibilités en matière d’efficacité énergétique et de mémoire pour une informatique plus performante.

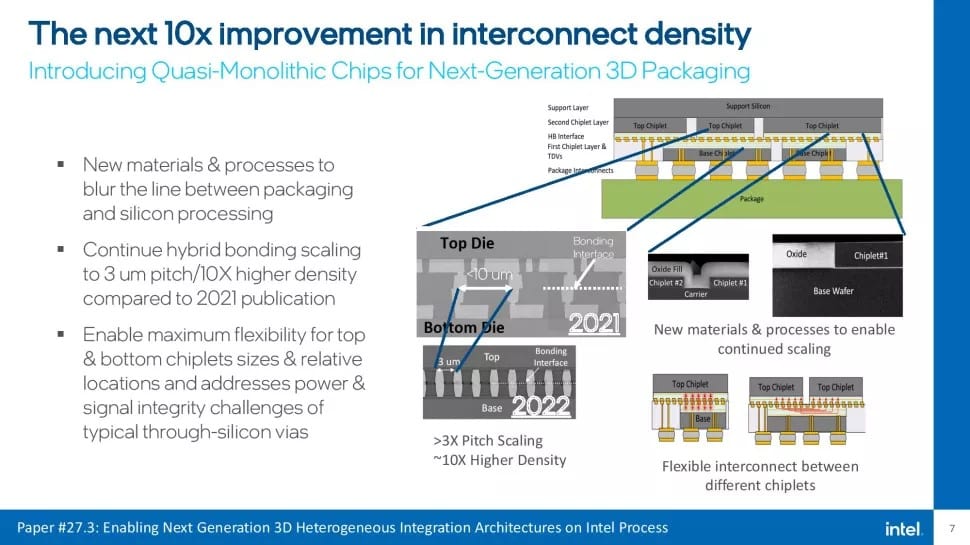

QMC : Quasi-Monolithic Chips

QMC est une nouvelle technique de collage hybride qui présente des pas inférieurs à 3 microns et permet de multiplier par 10 l’efficacité énergétique et la densité par rapport aux recherches qu’Intel a présentées à l’IEDM de l’année dernière. L’approche de 2021 utilisait des pas de 10 microns, ce qui représentait déjà une amélioration de 10 fois par rapport à l’année précédente. En d’autres termes, Intel prétend avoir réalisé un x100 en seulement deux ans, et pas cela ne relève pas des cryptos.

Le document décrit des densités d’interconnexion de centaines de milliers par millimètre carré et une consommation d’énergie (mesurée en picojoules par bit – Pj/b) rivalisant avec ce que nous voyons dans les processeurs monolithiques, grâce à de nouveaux matériaux et processus.

Les chercheurs rapportent ainsi avoir identifié le moyen de “brouiller la frontière entre l’emballage et le silicium”. Leur promesse : un billion (mille milliards, 10 puissance 12) de transistors dans un même boîtier.

Bientôt des PCB fabriqués à partir de champignons ?

Au-delà du RibbonFET

Intel désigne sa conception GAA sous le nom de RibbonFET. Elle doit être opérationnelle en 2024. Pour aller au-delà du RibbonFET, Intel explore la voie de la miniaturisation 2D.

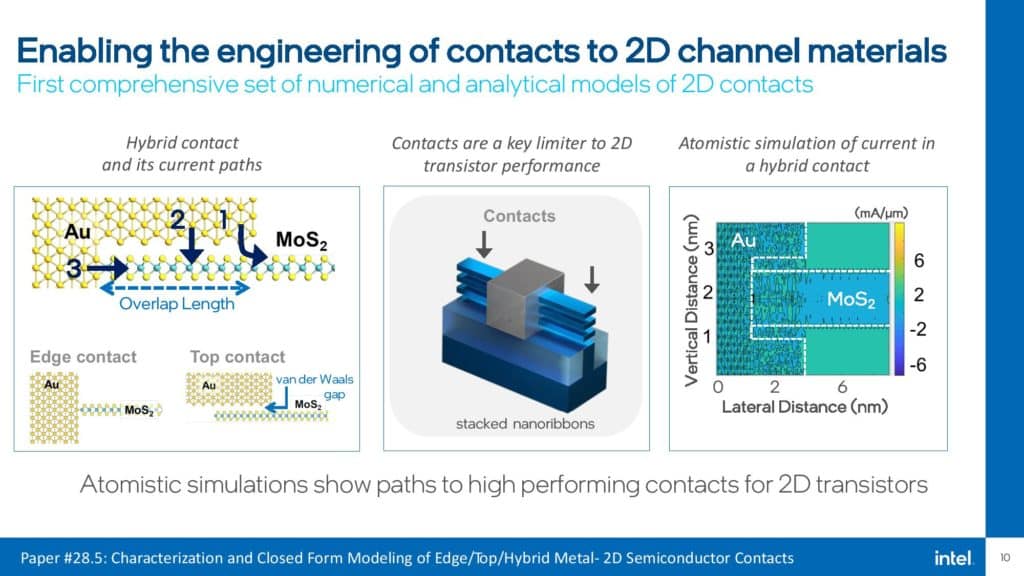

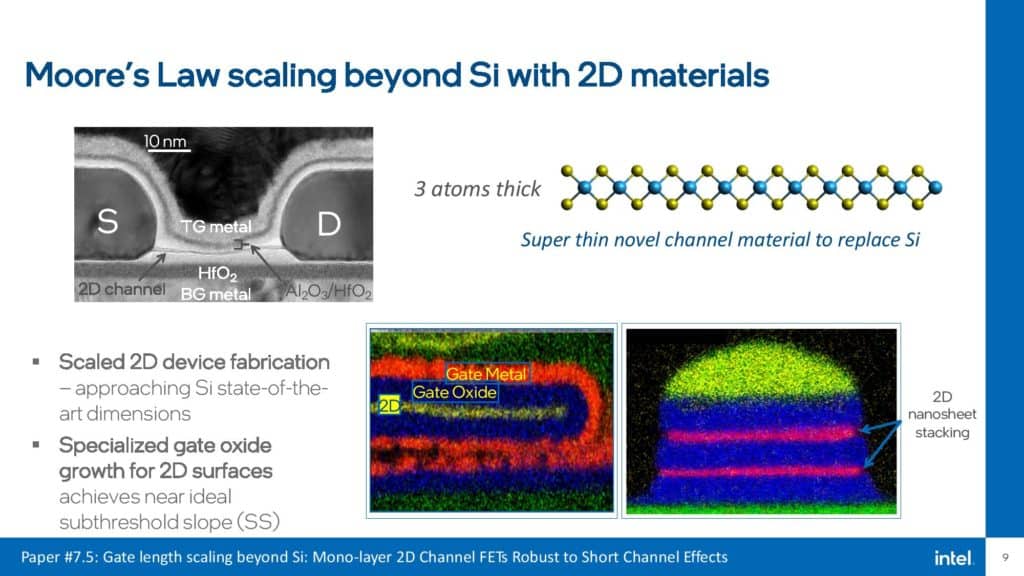

Concernant les transistors, la mise à l’échelle au-delà du RibbonFET serait rendue possible grâce à “un nouveau matériau de seulement 3 atomes d’épaisseur”. Concrètement, Intel a fait la démonstration d’une structure de nanofeuille empilée à grille complète utilisant un matériau de canal 2D de seulement 3 atomes d’épaisseur, tout en réalisant une commutation qualifiée de “quasi idéale” des transistors sur une structure à double grille à température ambiante avec un faible courant de fuite. Selon l’entreprise, ce sont là “deux percées essentielles pour empiler les transistors GAA et dépasser les limites fondamentales du silicium”.

Vers des transistors “non volatils”

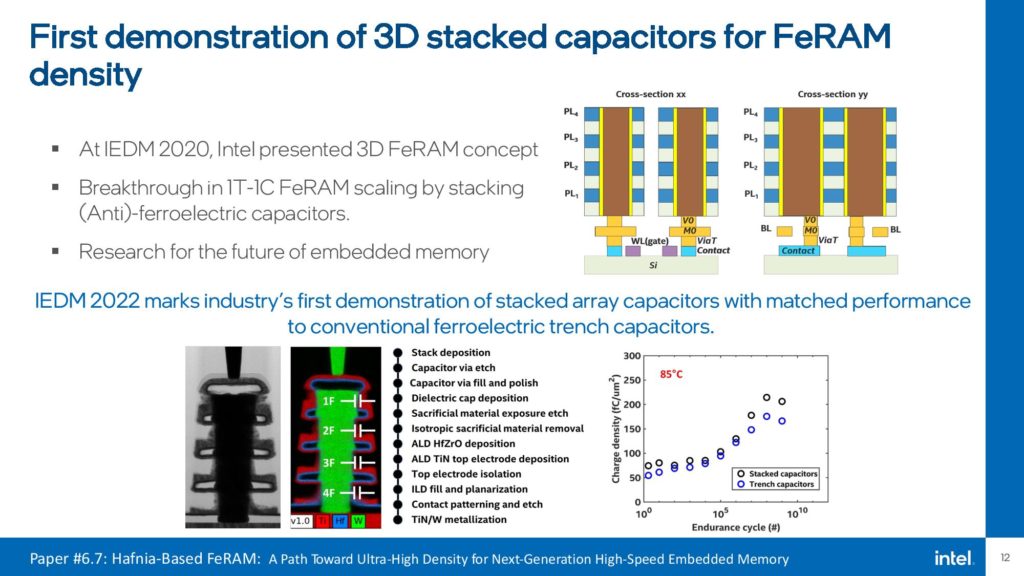

En matière de mémoire, Intel a réalisé la première démonstration au monde d’une mémoire ferroélectrique empilée en 3D fonctionnelle. La particularité : les condensateurs ferroélectriques peuvent être empilés verticalement sur la puce logique, au-dessus des transistors. Cela permet de superposer la mémoire aux éléments logiques au lieu de la placer dans une région distincte, comme c’est le cas avec d’autres types de mémoire intégrée, tels que la SRAM des caches L1 et L2.

Cette mémoire ferroélectrique jouit d’une particularité de la mémoire flash NAND, à savoir sa capacité à stocker plusieurs bits de données – en l’occurrence, quatre bits – dans une structure qui ne stocke généralement qu’un seul bit. Cette approche pourrait contribuer à augmenter à la fois la bande passante et la densité de la mémoire tout en réduisant la latence.

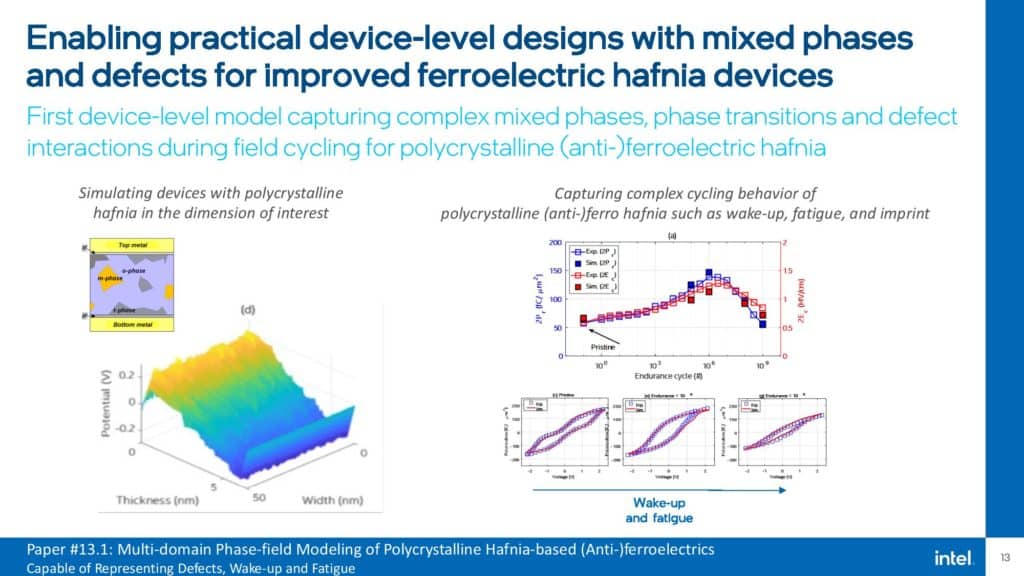

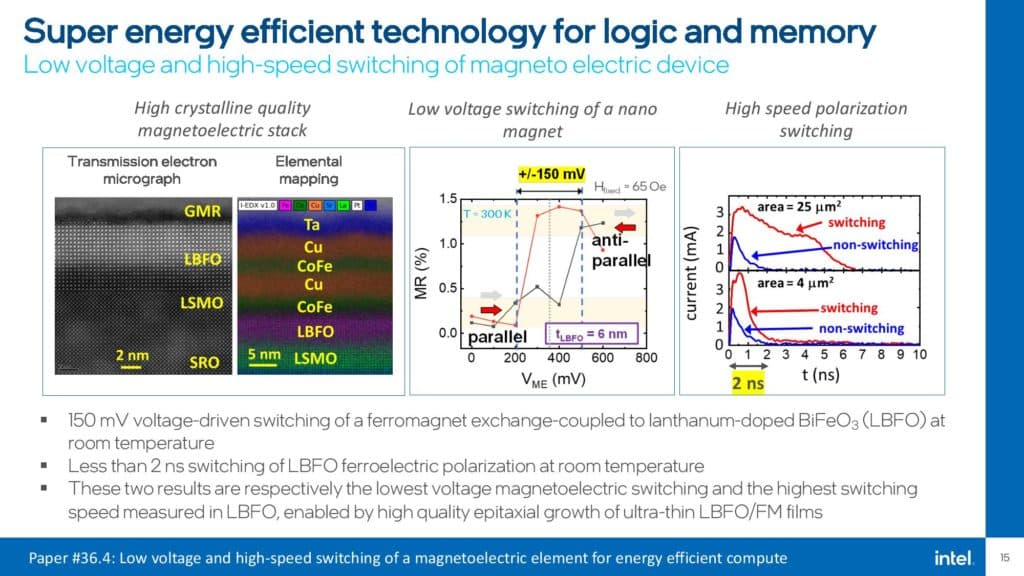

Enfin, Intel mène également des recherches sur des transistors qui “n’oublient pas”, c’est-à-dire qui ne perdent pas leurs données lorsqu’ils sont privés d’alimentation, à la manière du stockage non volatil type NAND. Intel affirme avoir surmonté “deux des trois obstacles” indispensables à l’application d’une telle caractéristique à température ambiante à des transistors logiques.

Source : Intel