Une première version, le N2, en 2025, sans BPD (backside power delivery), puis du N2P avec BPD l’année suivante. De son côté, Intel prévoit de graver en 2 nm dès l’année prochaine, et prendrait donc deux ans d’avance sur TSMC…

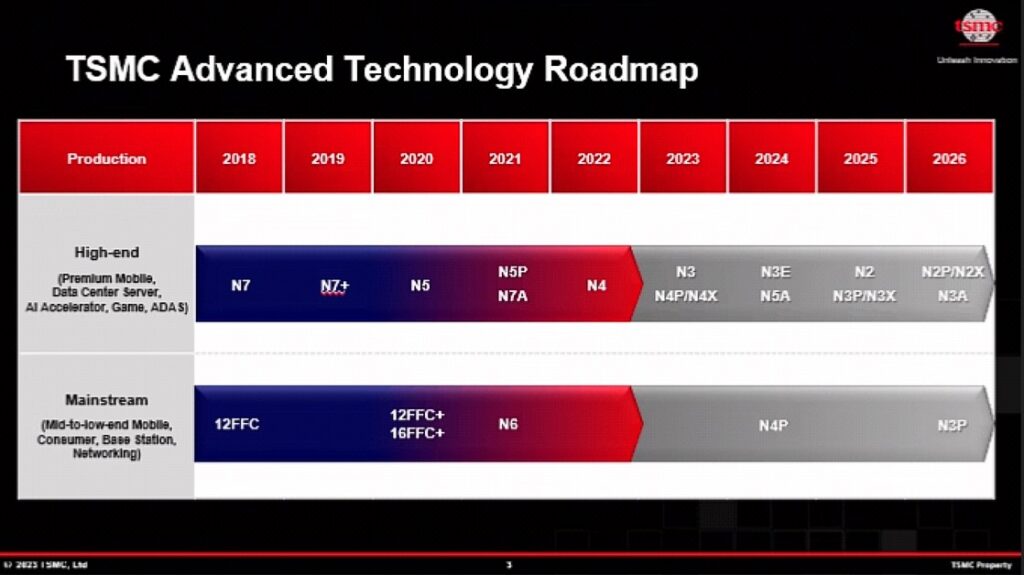

À l’occasion de sa North American Technology Symposium 2023, le fondeur taïwanais TSMC a détaillé ses prochaines nœuds de gravure 2 nm. L’entreprise grave actuellement en 3 nm, et le passage à la famille N2 n’est pas prévu dans l’immédiat : il interviendra en 2025 / 2026 selon la feuille de route du fondeur.

TSMC prévoit trois nœuds de gravure pour le moment : le N2, le N2P et le N2X. Jusqu’ici, l’entreprise se limitait à évoquer le N2. Ces finesses de gravure introduiront des transistors à feuillets nanométriques (gate-all-around, GAA). Ils permettront de réduire la consommation d’énergie et / ou d’augmenter la densité de transistors.

À lire > Samsung Electronics espère graver en 2 nm dès 2025, puis en 1,4 nm en 2027

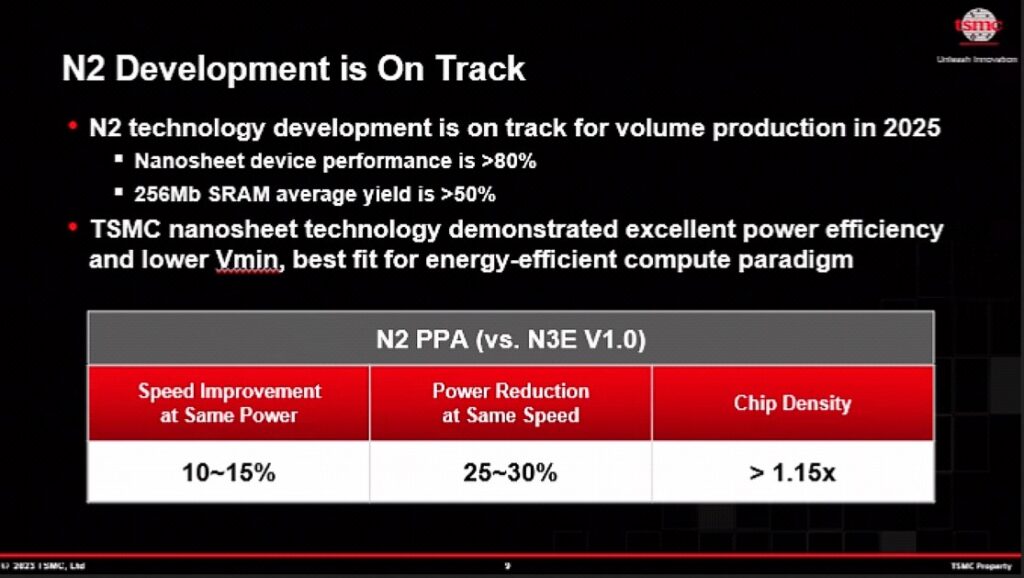

Les gains offerts par le 2 nm

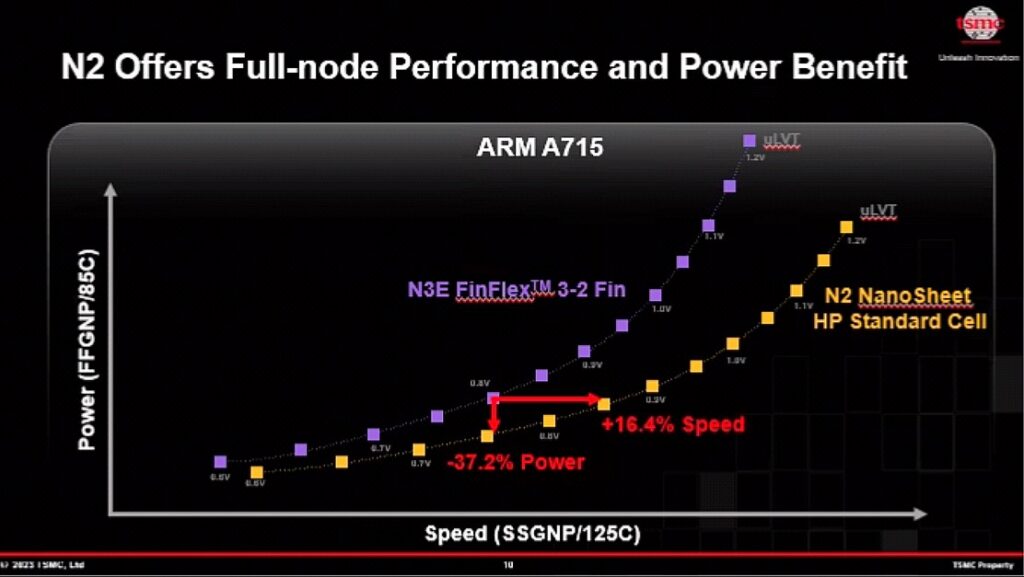

Par rapport au N3, le N2 augmentera les performances de 10 à 15 % à puissance et quantité de transistors identiques ; réduira la consommation d’énergie de 25 à 30 % à fréquence et complexité égales. En matière de densité, le fondeur renseigne une hausse de 15 %. TSMC précise également que les tests se déroulent bien : la société rapporte que les transistors Nanosheet GAA ont atteint plus de 80 % des spécifications cibles et que le rendement moyen d’un circuit de test SRAM de 256 Mb dépassait 50 %.

Le N2P, soit la deuxième génération, doit s’appuyer sur un rail d’alimentation arrière pour améliorer les performances. Comme le souligne Anton Shilov de Tom’s Hardware US, l’alimentation par l’arrière marquera l’une des étapes les plus importantes de ces dernières années. Notre confrère explique que déplacer les rails d’alimentation à l’arrière du wafer permet de séparer le câblage d’E/S et le câblage d’alimentation et atténue ainsi les problèmes de résistance dans le BEOL (back end of line). TSMC ne chiffre pas les gains offerts par le N2P par rapport au N2. Selon certains analystes, ce rail d’alimentation arrière pourrait entraîner une baisse à un chiffre de la consommation d’énergie et une augmentation à deux chiffres de la densité des transistors.

Concernant le N2X, ce sera un processus essentiellement destiné à produire des processeurs HPC devant supporter des tensions très élevées.

Pour finir, rappelons qu’Intel ambitionne de finaliser son nœud de gravure 20A avec transistors RibbonFET GAA et PowerVia en 2024, soit avec au moins deux d’avance sur TSMC…

Sources : Tom’s Hardware US, SemiWiki