Par rapport au 5 nm, ce nœud 3GAE réduit la consommation de 45 %, la surface de 16 %, et améliore les performances de 23 %.

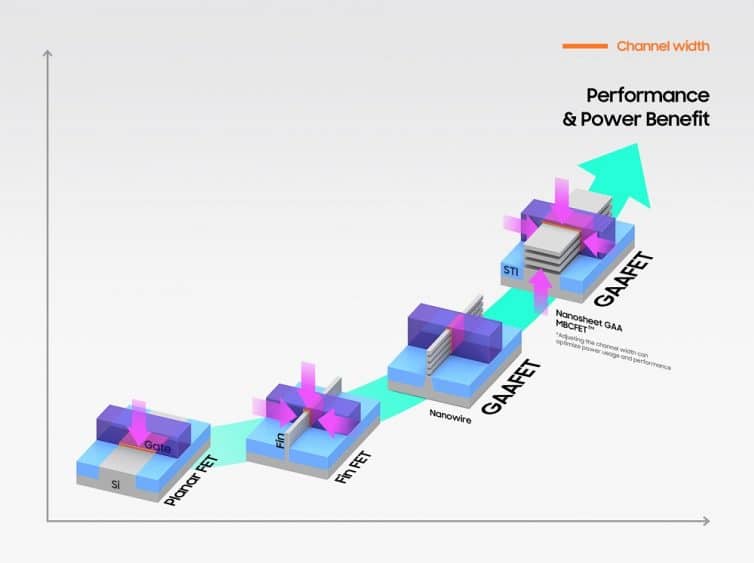

Comme prévu, Samsung a initié la production de masse en 3 nm. Ce nœud 3GAE implique des transistors Gate-All-Around (GAA). Selon la firme coréenne, par rapport au processus 5 nm, cette technologie Multi-Bridge-Channel FET (MBCFET) réduit de 45 % la consommation d’énergie, la surface de 16 %, améliore les performances de 23 %.

Samsung argue que sa technologie à base de nanofeuilles facilite l’ajustement de la largeur du canal afin d’optimiser l’utilisation de l’énergie et les performances pour répondre aux différents besoins des clients. À l’instar de TSMC, Samsung met en avant un écosystème complet, ici baptisé SAFE, acronyme de Samsung Advanced Foundry Ecosystem.

La société explique : “À mesure que les nœuds technologiques se réduisent et que les besoins en matière de performances des puces augmentent, les concepteurs de circuits intégrés doivent relever le défi de traiter d’énormes quantités de données pour vérifier des produits complexes comportant davantage de fonctions et une mise à l’échelle plus étroite. Pour répondre à ces exigences, Samsung s’efforce de fournir un environnement de conception plus stable afin de réduire le temps nécessaire aux processus de conception, de vérification et de validation, tout en améliorant la fiabilité des produits”. Avec l’aide des partenaires, notamment Ansys, Cadence, Siemens et Synopsys, le SAFE doit aider les clients “à perfectionner leur produit dans un délai réduit”.

En attendant le 3 nm de deuxième génération

Ce 3GAE (E pour early) n’est qu’une première étape pour le 3 nm. Les gains évoqués en début d’article valent pour ce processus. Celui de deuxième génération permettra de réduire la consommation d’énergie jusqu’à 50 %, d’améliorer les performances de 30 % et de réduire la surface de 35 % promet Samsung.

TSMC dévoile sa feuille de route jusqu’en 2025 : cap sur le 2 nm

Déclaration

Le communiqué de Samsung contient plusieurs déclarations. Pour n’en citer qu’une, Tom Beckley, vice-président senior et directeur général du groupe Custom IC & PCB chez Cadence, rapporte :

“Nous félicitons Samsung pour cette étape importante de la mise en production du GAA 3nm. Cadence a travaillé en étroite collaboration avec Samsung Foundry pour permettre aux clients d’obtenir une puissance, des performances et une surface optimales pour ce nœud en utilisant nos solutions numériques, de la caractérisation des bibliothèques à la mise en œuvre et à la validation du flux numérique complet, le tout piloté par notre technologie Cadence Cerebrus basée sur l’intelligence artificielle pour maximiser la productivité. Grâce à nos solutions personnalisées, nous avons collaboré avec Samsung pour activer et valider un flux AMS complet afin d’améliorer la productivité, de la conception et la simulation de circuits à la mise en page automatisée. Nous sommes impatients de poursuivre cette collaboration pour obtenir de nouveaux succès en matière de tape-out” (le tape-out désigne l’ultime étape du processus de conception des circuits intégrés, juste avant la fabrication).

Source : Samsung