Un récent brevet dévoile une conception de ce type appliquée aux GPU.

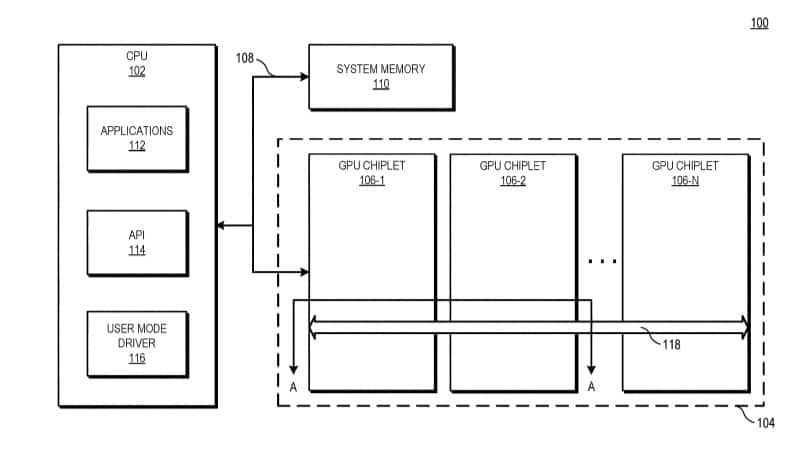

Depuis l’avènement de l’architecture CPU Zen 2, pour ses processeurs, AMD a abandonné une conception dite monolithique au profit d’une solution modulaire sous forme de chiplets. Cela a notamment permis d’augmenter le nombre de cœurs CPU tout en réduisant les coûts. Selon un récent brevet, publié le 31 décembre, AMD envisagerait une architecture similaire pour ses GPU.

En théorie, ce type d’architecture devra être généralisée, y compris sur des GPU, pour continuer d’honorer la loi de Moore ; la miniaturisation a ses limites. Néanmoins, adopter une conception MCM (Multi-Chip Module) sur les cartes graphiques est plus délicat que sur les processeurs. En effet, fragmenter les cœurs CPU dans plusieurs chiplets qui communiquent entre eux est moins ardu que pour des cœurs GPU, plus étroitement imbriqués. La raison : les charges de travail GPU s’y prêtent moins bien que les charges de travail CPU, lesquelles sont traitées de manière plus indépendantes par chaque cœur CPU. De manière schématique, séparer les cœurs CPU sur plusieurs chiplets s’apparente, caricaturalement, à faire collaborer plusieurs processeurs, comme dans une configuration multi-sockets ; pour les GPU, l’analogie équivalente ressemblerait à des GPU configurés en SLI ou en CrossFire.

Un Ryzen 3950X monolithique coûterait environ 1700 dollars

Assurer une bonne communication interne et externe

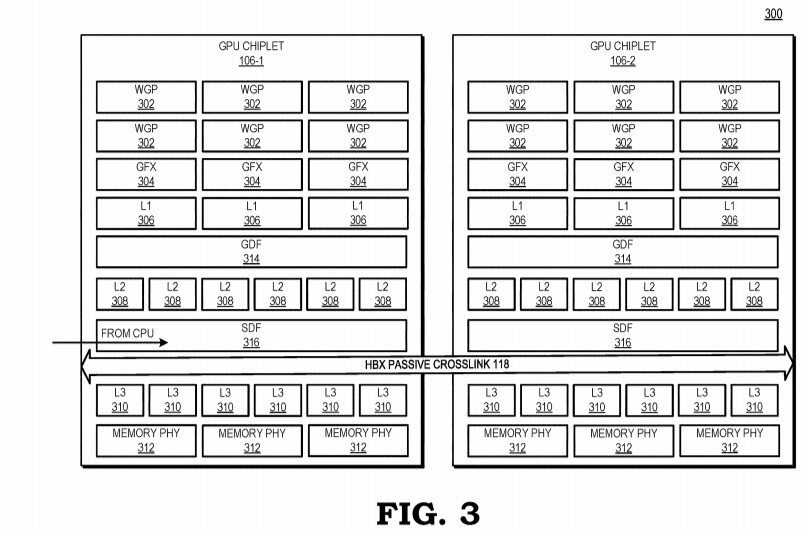

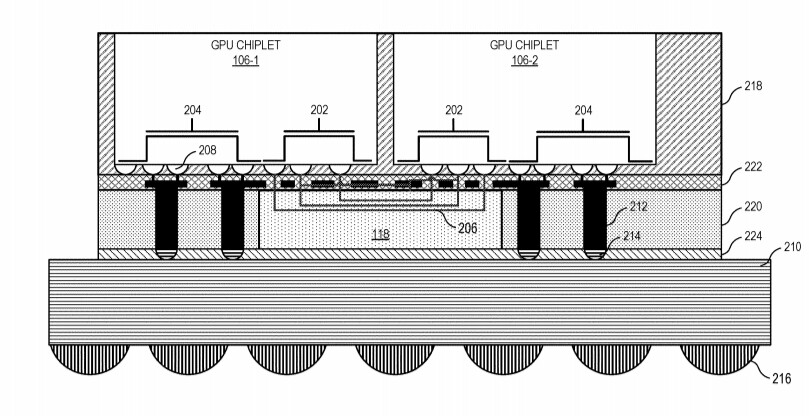

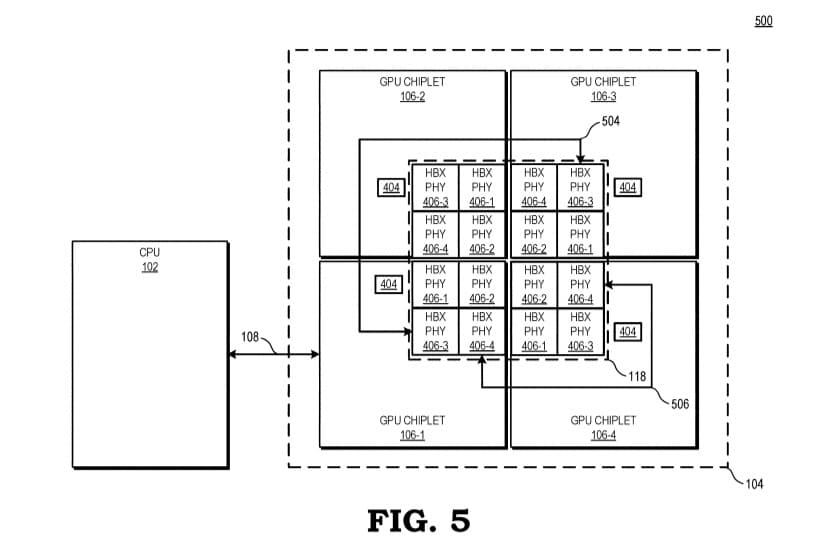

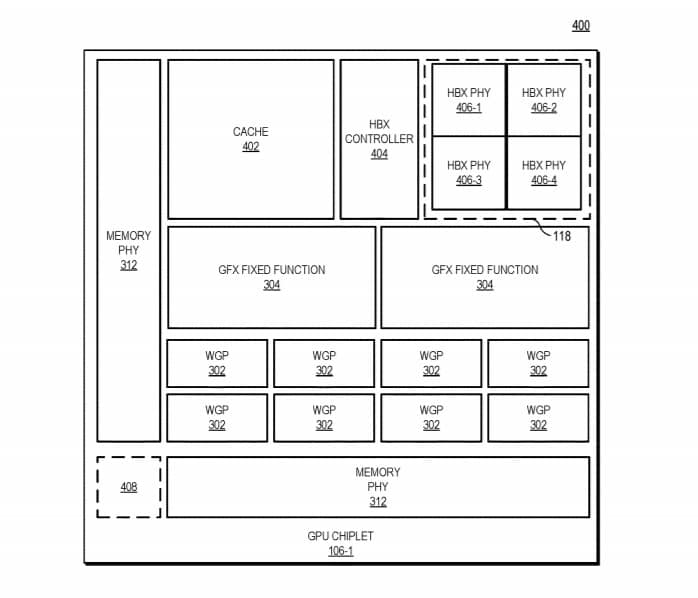

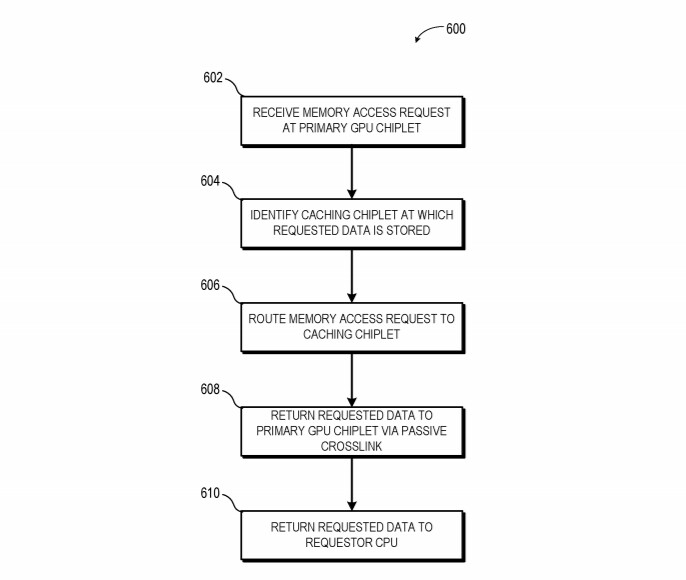

Assurer une bonne communication interne entre les cœurs GPU est la principale difficulté d’une conception MCM GPU. Pour la résoudre, AMD opterait pour une interconnexion à large bande passante. Sur un plan physique, ce canal ressemble à l’interposer des CPU Zen 3. Toute la communication interne passerait par cet interposer. Le brevet suggère également que chaque chiplet aurait son propre LLC (Last Level Cache).

Par ailleurs, pour que cette conception MCM soit viable, elle doit être compatible avec les langages existants et ne nécessiter que quelques menus ajustements de pilotes avec les logiciels actuels. Comme pour les processeurs Ryzen, elle doit également être modulable et évolutive, avec par exemple 4 ou 2 chiplets.

Cette architecture pourrait être mise en œuvre après RDNA 3 ; autrement dit, pas avant plusieurs années.