Aucun changement majeur ou nouvelles fonctionnalités ne peuvent être apporté ni ajoutées désormais.

Alors que le PCIe 4.0 est encore loin de brider nos cartes graphiques et SSD et que le PCIe 5.0 va tout juste faire ses débuts avec la plateforme Alder Lake, le PCI-SIG vient de passer la spécification PCIe 6.0 en version 0.9 ; une étape qui marque la fin du développement de la norme. Pour retracer brièvement ce parcours, l’organisme avait annoncé dès 2019 que le PCIe 6.0 serait finalisé en 2021. En février 2020 il avait atteint la version 0.5 puis en novembre de la même année, la version 0.7.

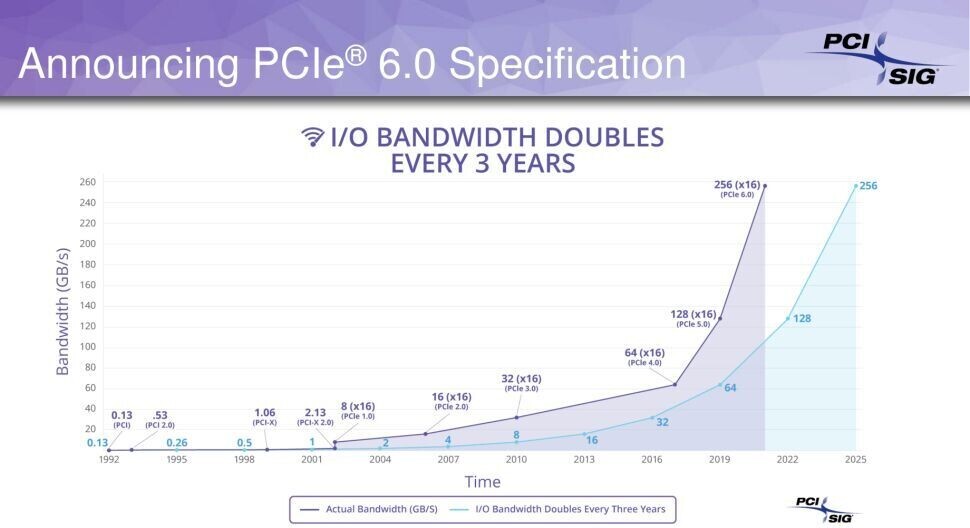

Comme à chaque nouvelle génération, le PCIe 6.0 promet des débits doublés par rapport au PCIe 5.0 : 64 GT/s par ligne contre 32 GT/s pour le PCIe 5.0 et 16 GT/s pour le PCIe 4.0 actuel. En pratique, le PCIe 6.0 autorisera une vitesse de transfert de 128 Go/s en x16.

Phison présente son contrôleur E26 pour les SSD en PCIe 5.0

PAM-4

La finalisation d’une norme PCIe se fait en cinq étapes : conception, première version partielle, version complète, version finale et version définitive. À partir de la version 0.7, les entreprises peuvent commencer à travailler sur la mise en œuvre de la norme. La version 0.9, dernière étape avant la finalisation, n’autorise plus aucun changement fonctionnel. Désormais, il s’agit surtout d’établir le programme officiel de conformité.

Comme nous l’avions expliqué dans une précédente actu, l’une des principales nouveautés du PCIe 6.0 est le recours à l’encodage PAM-4 (Pulse Amplitude Modulation sur 4 niveaux) à la place du NRZ 128b/130b utilisé depuis le PCIe 3.0. Par rapport au NRZ, celui-ci double le nombre d’états électriques qu’une seule cellule peut contenir. Plutôt que le traditionnel 0/1, PAM-4 utilise quatre niveaux par signal. Un signal peut ainsi coder quatre configurations possibles de deux bits : 00/01/10/11. Cela permet au PAM-4 de transporter deux fois plus de données que le NRZ sans avoir à doubler la bande passante de transmission.

Revers de la médaille, le PAM-4 a des répercussions sur la taille des puces et la consommation. En pratique, la mise en œuvre du PCIe 6.0 entraînera d’importants surcoûts et en conséquence, cette interface ne débarquera pas sur les plateformes grand public de sitôt.