AMD devrait lancer ses processeurs AMD Zen 6 de série 10 000 avec les processus de gravure de 2 nm et de 3 nm de TSMC, courant 2026.

AMD prépare activement sa prochaine génération de processeurs, basée sur l’architecture Zen 6. Selon des informations récentes et des documents partagés avec des partenaires industriels, ces puces utiliseront une combinaison des procédés de fabrication N2P (2 nm) et N3P (3 nm) de TSMC, avec une sortie prévue à partir de la fin 2026. Cette stratégie vise à optimiser performances, efficacité énergétique et coûts, selon les segments ciblés (desktop, mobile, serveur).

Une architecture hybride pour répondre à tous les segments

Les processeurs Zen 6 se distingueront par l’utilisation différentielle des nœuds de production :

- N2P (2 nm) : réservé aux Core Complex Die (CCD), c’est-à-dire les puces abritant les cœurs de calcul. Ce procédé permettra d’augmenter la densité de transistors et d’améliorer l’efficacité énergétique.

- N3P (3 nm) : utilisé pour les I/O Die (IOD), qui gèrent la mémoire, les entrées/sorties (PCIe, USB) et, le cas échéant, le GPU intégré. Ce choix vise à maîtriser les coûts tout en bénéficiant d’une technologie mature.

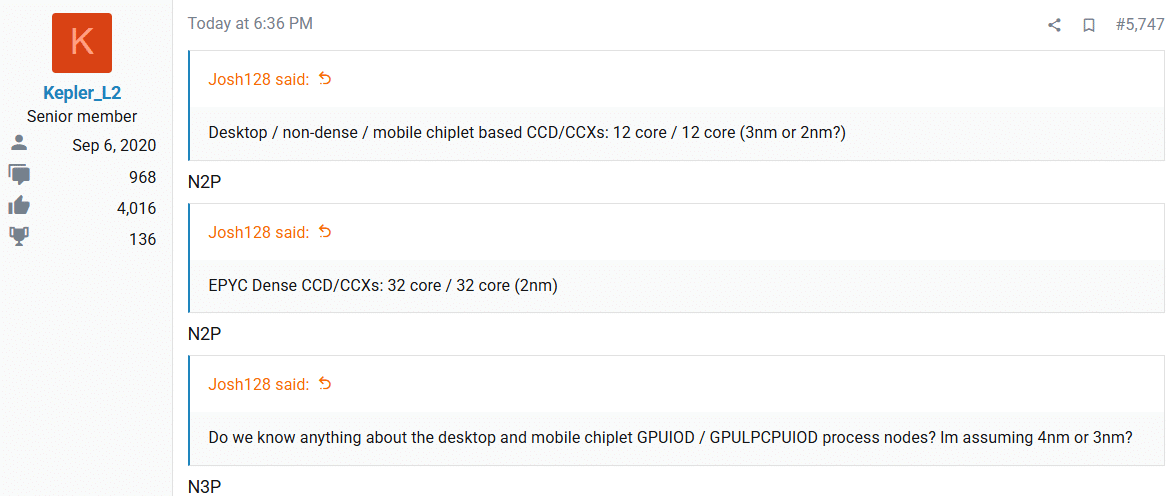

Cette approche a été confirmée par plusieurs sources, dont des fuites crédibles relayées par des leakers reconnus (Kepler_L2, Adroc_thurston) et des documents internes partagés avec des fabricants de cartes mères. AMD et TSMC ont collaboré étroitement pour adapter les bibliothèques de cellules et les couches métalliques, aboutissant à une implémentation parfois qualifiée de “N2-AMD”, optimisée spécifiquement pour les besoins du fondeur.

Détail des gammes et des plateformes

Les processeurs Zen 6 couvriront l’ensemble des segments :

- Desktop : la série Olympic Ridge (Ryzen 10000) utilisera le N2P pour les CCD, avec une compatibilité maintenue avec la plateforme AM5, un avantage face à Intel, dont les Nova Lake-S nécessiteront une nouvelle socket (LGA 1954).

- Mobile : la gamme Medusa Point adoptera une approche hybride, combinant un CCD en N2P et un IOD en N3P pour les modèles haut de gamme, tandis que les entrées de gamme se contenteront d’un die monolithique en N3P.

- Serveur : les EPYC Venice Classic et Venice Dense utiliseront exclusivement le N2P, avec des CCD pouvant intégrer jusqu’à 32 cœurs (contre 12 pour les versions grand public), et des fréquences visées au-delà de 6 GHz.

Calendrier et production

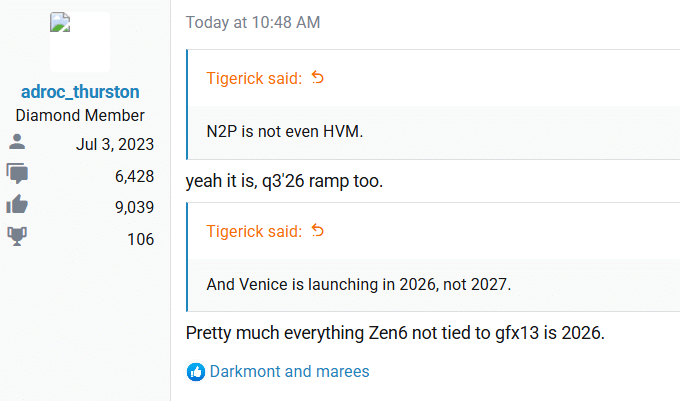

- Fin 2025 : retour des premiers échantillons (first silicon) depuis les usines.

- Troisième trimestre 2026 : début de la production en volume (HVM) du N2P, permettant une disponibilité commerciale dès le quatrième trimestre 2026, d’abord en quantités limitées.

- 2027 : montée en puissance progressive, avec une vague de rafraîchissement pour les serveurs et les portables en rentrée scolaire.

AMD mise sur l’expérience acquise avec TSMC pour éviter les problèmes de rendement, le N2P bénéficiant d’une rampe de production accélérée par rapport aux générations précédentes.

La concurrence avec Intel est sérieuse

Zen 6 arrivera sur un marché où Intel déploiera ses Nova Lake-S, avec jusqu’à 52 cœurs. La rétrocompatibilité avec l’AM5 et l’optimisation des procédés pourraient donner à AMD un avantage en termes de coût et de facilité de mise à niveau pour les utilisateurs existants. Les performances réelles, notamment en matière d’IPC (Instructions Per Cycle) et de fréquences, resteront à évaluer lors des tests indépendants. AMD n’a pas commenté ces rumeurs et fera son annonce en bonne et due forme le moment venu.