NVIDIA : résumé de la trentaine d’annonces faites à la GTC 2021

Des annonces dans les domaines de l’automobile, du supercalcul, et de la collaboration numérique ; mais le clou du spectacle, c'est Toy Jensen.

Deux supercalculateurs chinois auraient déjà franchi la barrière de l’exascale

Avec plusieurs mois d'avance sur le supercalculateur américain Frontier.

Intel annonce désormais 2 ExaFLOPS pour le supercalculateur Aurora

L'entreprise a également conclu un partenariat avec SiPearl pour équiper des supercalculateurs européens d'accélérateurs Ponte Vecchio.

TSMC ajoute un nœud de gravure, le N4P

Troisième amélioration majeure de la famille 5 nm aux dires de TSMC.

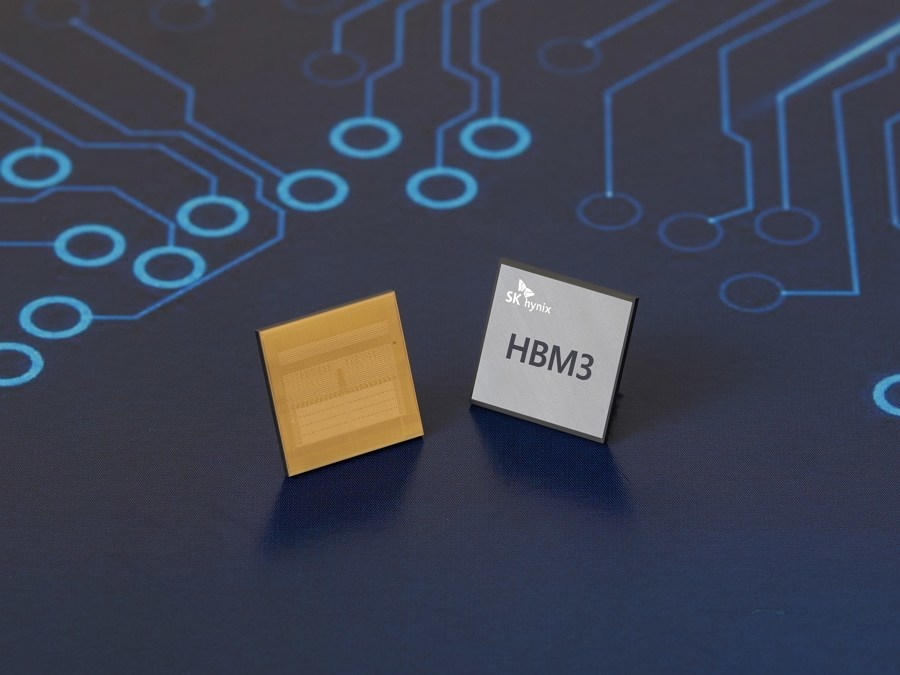

SK Hynix détaille sa DRAM HBM3 : jusqu’à 24 Go et 6,4 Gbit/s

Une bande passante par puce de 819 Go/s.

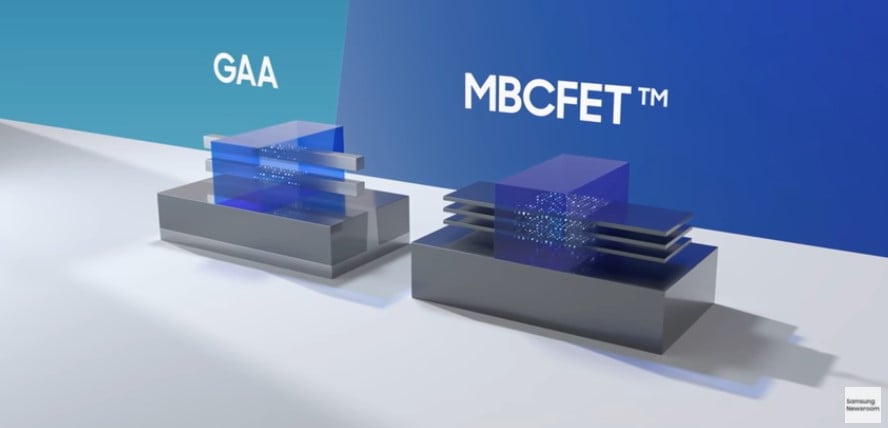

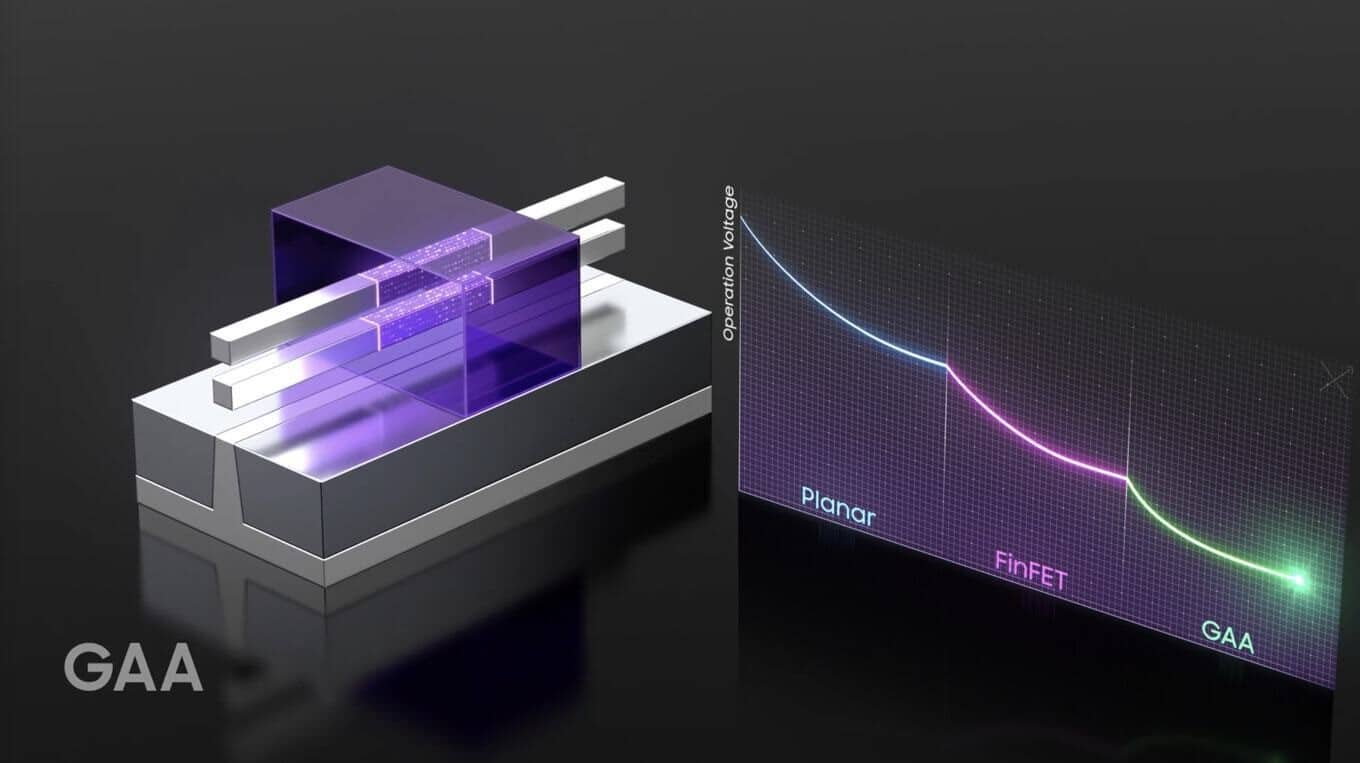

Samsung : le 3 nm l’année prochaine, le 2 nm en 2025

Le fondeur coréen amorce la transition vers des transistors GAA.

Le PCIe 6.0 passe en version 0.9, ultime étape avant sa finalisation

Aucun changement majeur ou nouvelles fonctionnalités ne peuvent être apporté ni ajoutées désormais.

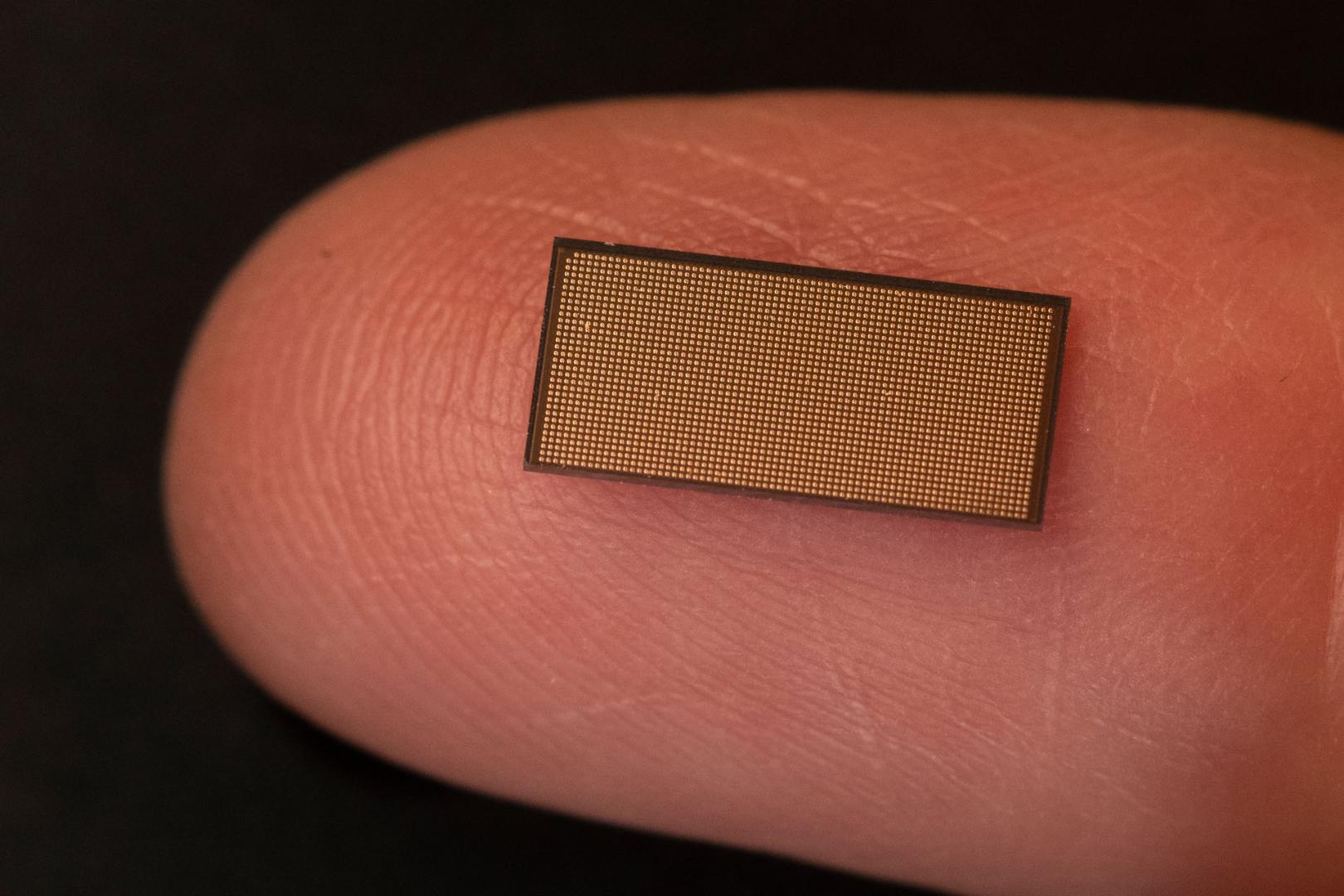

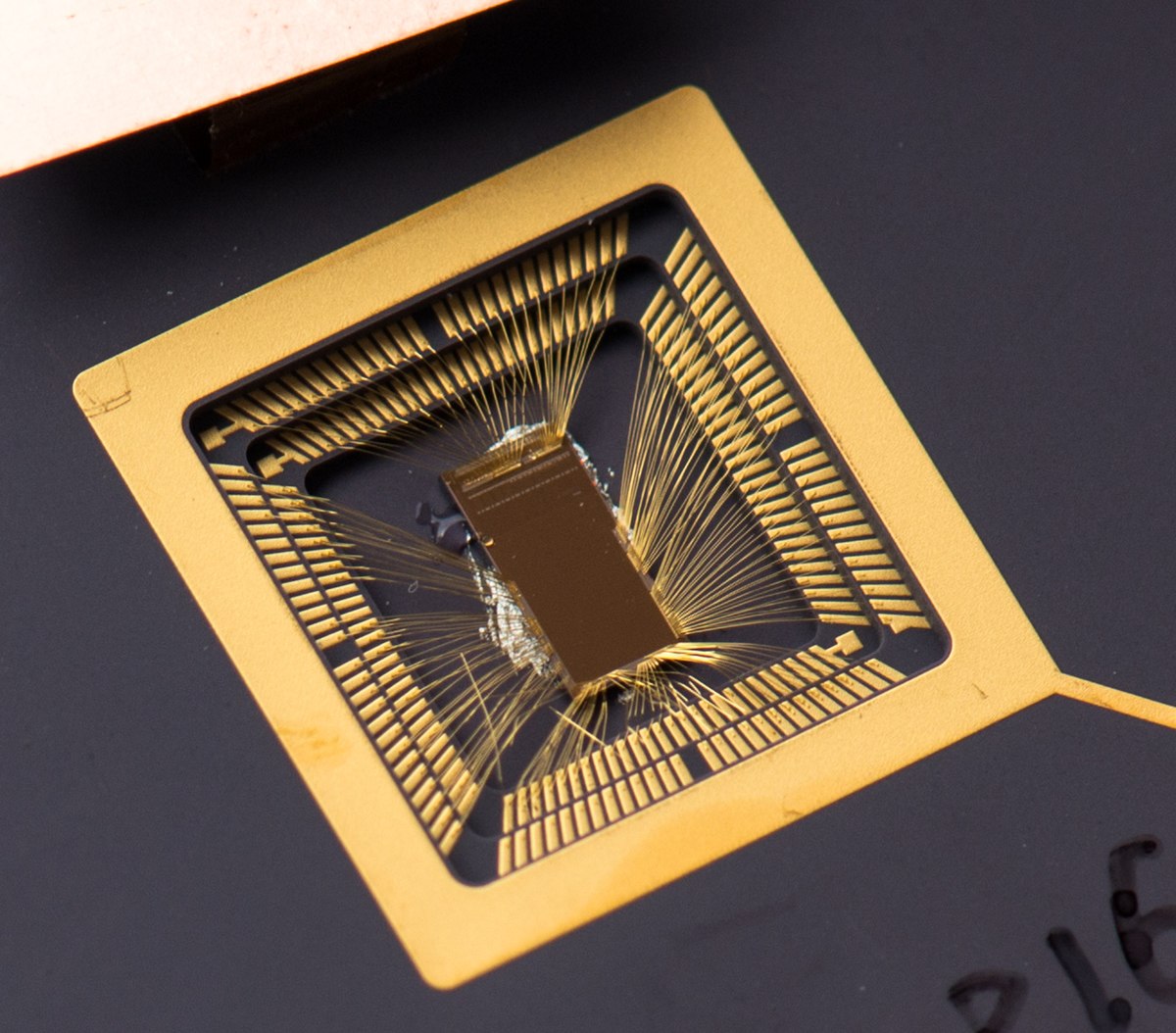

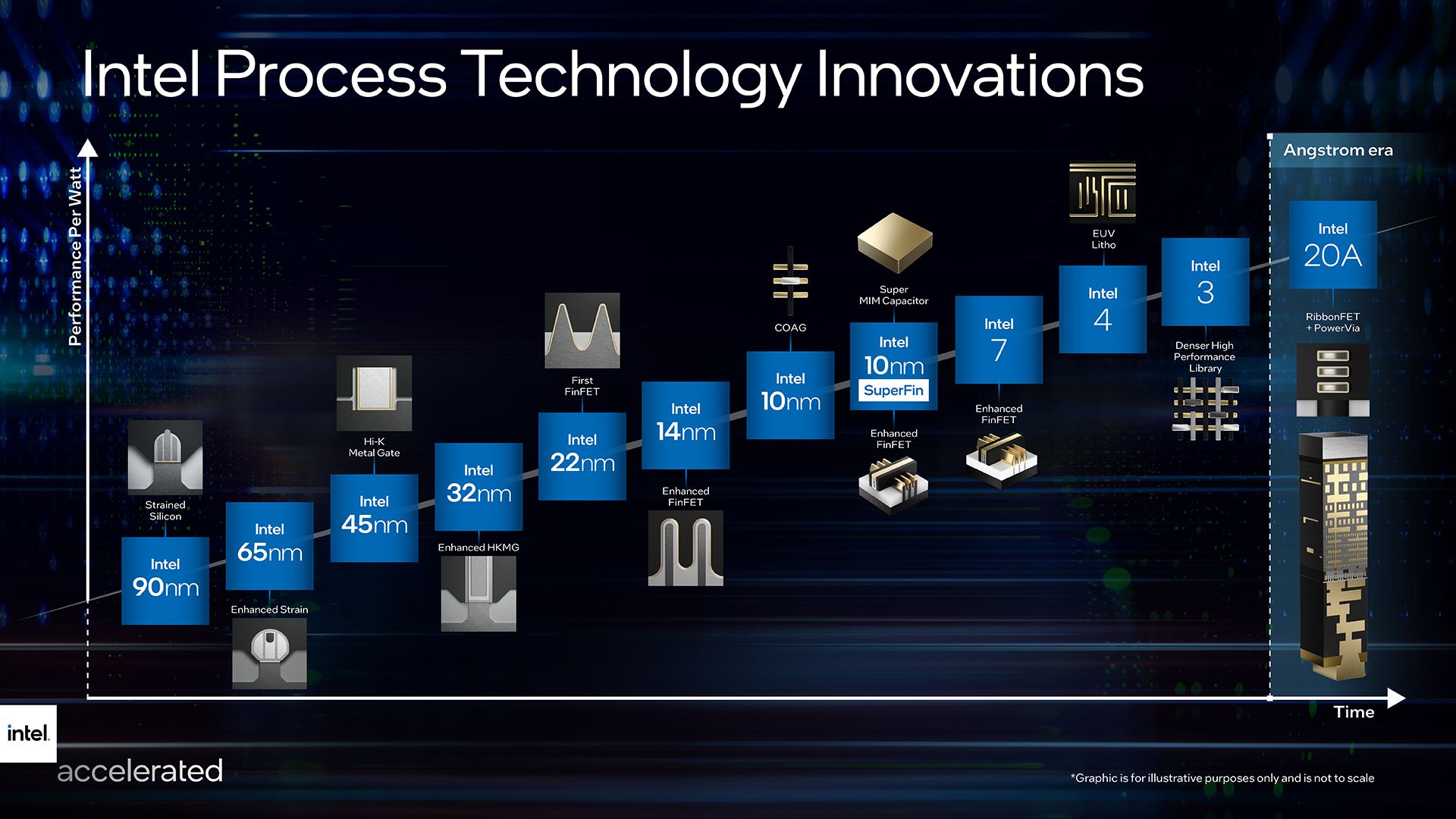

Intel présente Loihi 2, son processeur neuromorphique de deuxième génération

Une puce à un million de neurones programmables conçue sur le procédé de fabrication Intel 4 (7 nm EUV).

Grâce à un faisceau laser, le projet Taara a permis la transmission de 700 To de données sur une distance de 5 km

Sur vingt jours d’exploitation en Afrique, le taux de disponibilité s'élève à 99,9 %.

AMD est disposé à concevoir des puces ARM selon son directeur financier

Mais le cas échéant, l'entreprise ne ferait que répondre à une demande de ses clients.

Du NVIDIA CUDA à la sauce GPGPU RISC-V

Vortex, un projet qui permet une prise en charge de CUDA sur une architecture GPU RISC-V.

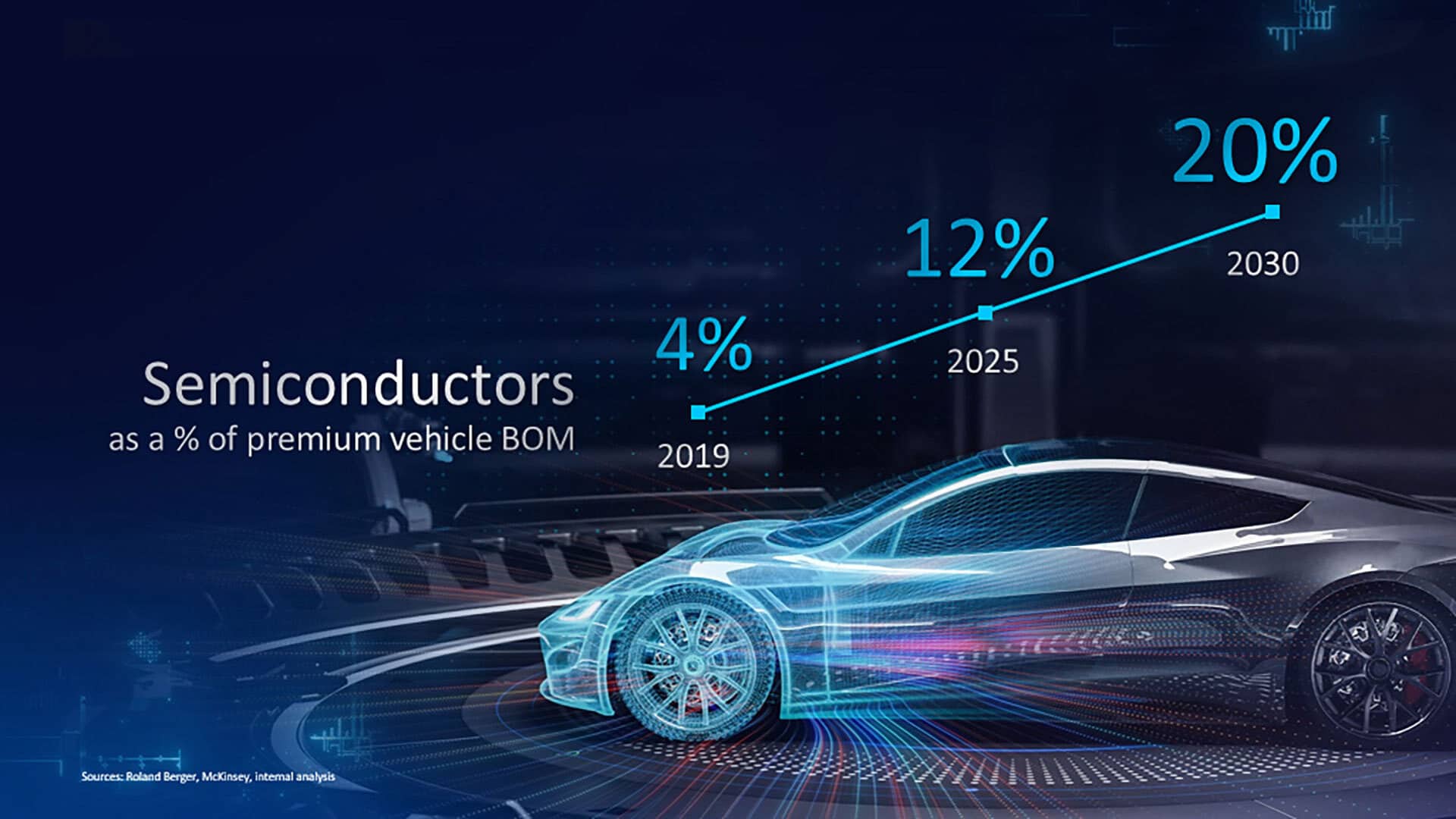

Pat Gelsinger pense que la part des semi-conducteurs dans la nomenclature des voitures atteindra 20 % en 2030

Elle n'était que de 4 % en 2019.

Apple lorgne aussi sur l’architecture RISC-V

À l’avenir, les puces Apple Silicon pourraient ne pas être circonscrites à l’architecture Arm.

Google développe ses propres processeurs pour Chromebook

La stratégie d’émancipation de Google en matière de puces ne se limitera pas aux seuls smartphones Pixel.

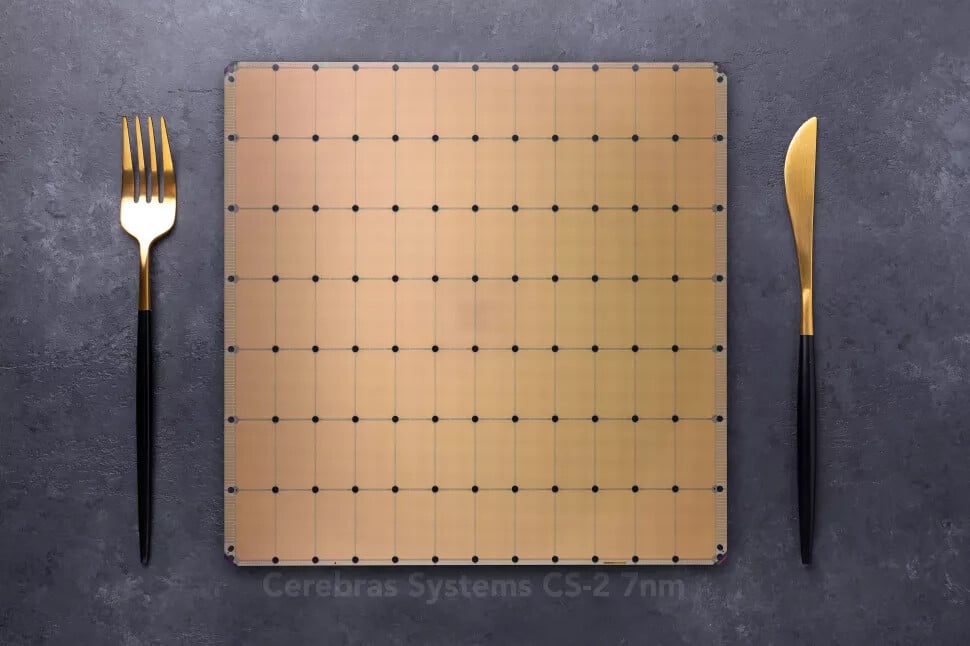

Cerebras peut associer jusqu’à 192 systèmes CS-2, soit 163 millions de cœurs

Un seul système CS-2 est capable de gérer une couche d'un réseau neuronal à 120 billions de paramètres.

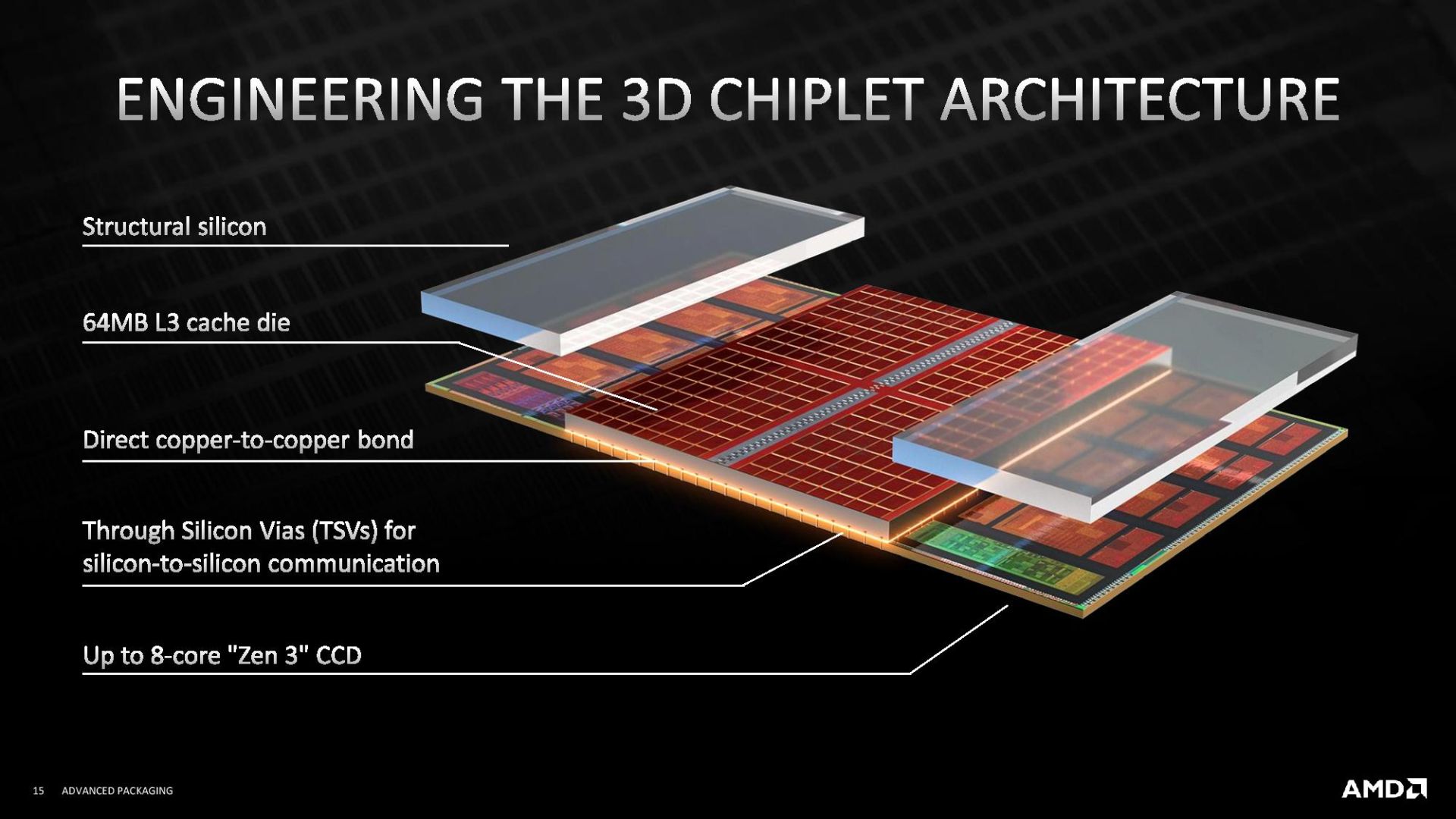

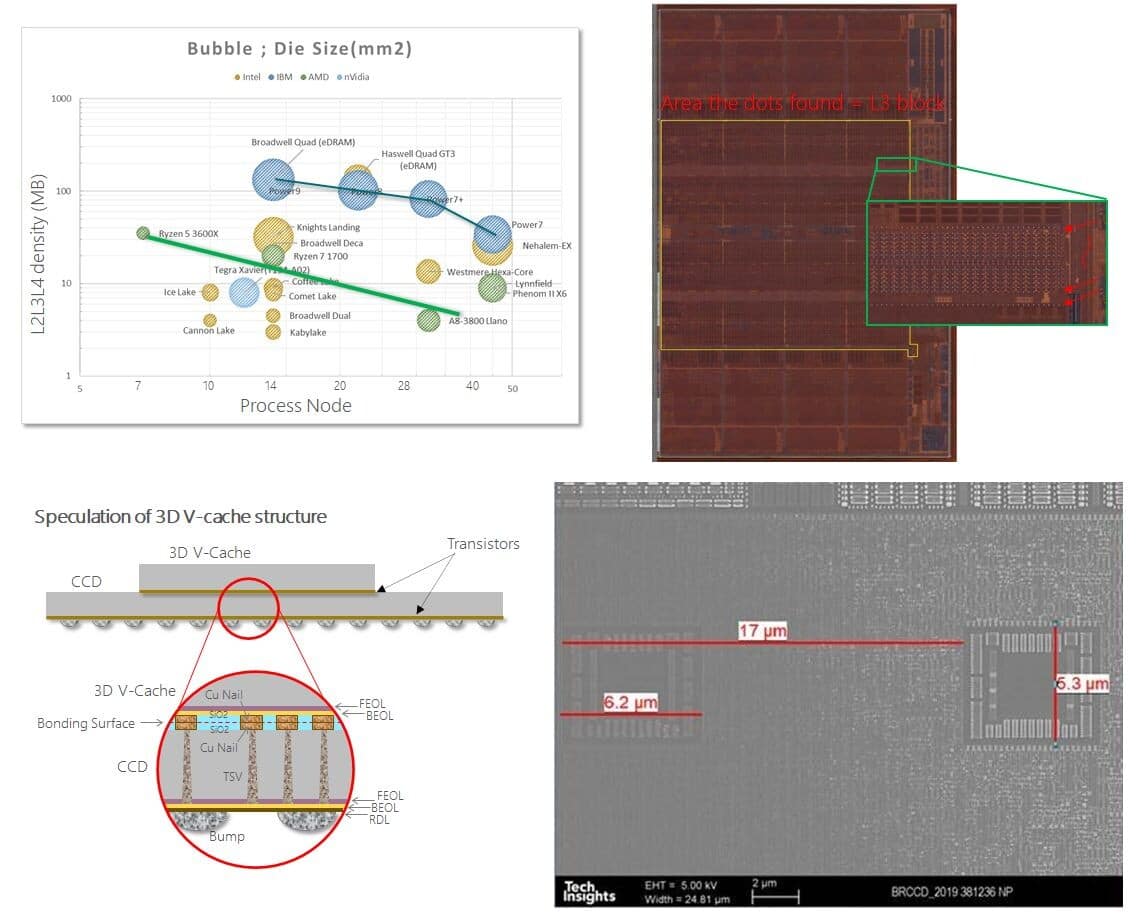

AMD détaille sa technologie 3D Chiplet

Des interconnexions TSV offrant une efficacité énergétique 3 fois plus élevée et une densité 15 fois supérieure à celles des micro-bosses 3D.

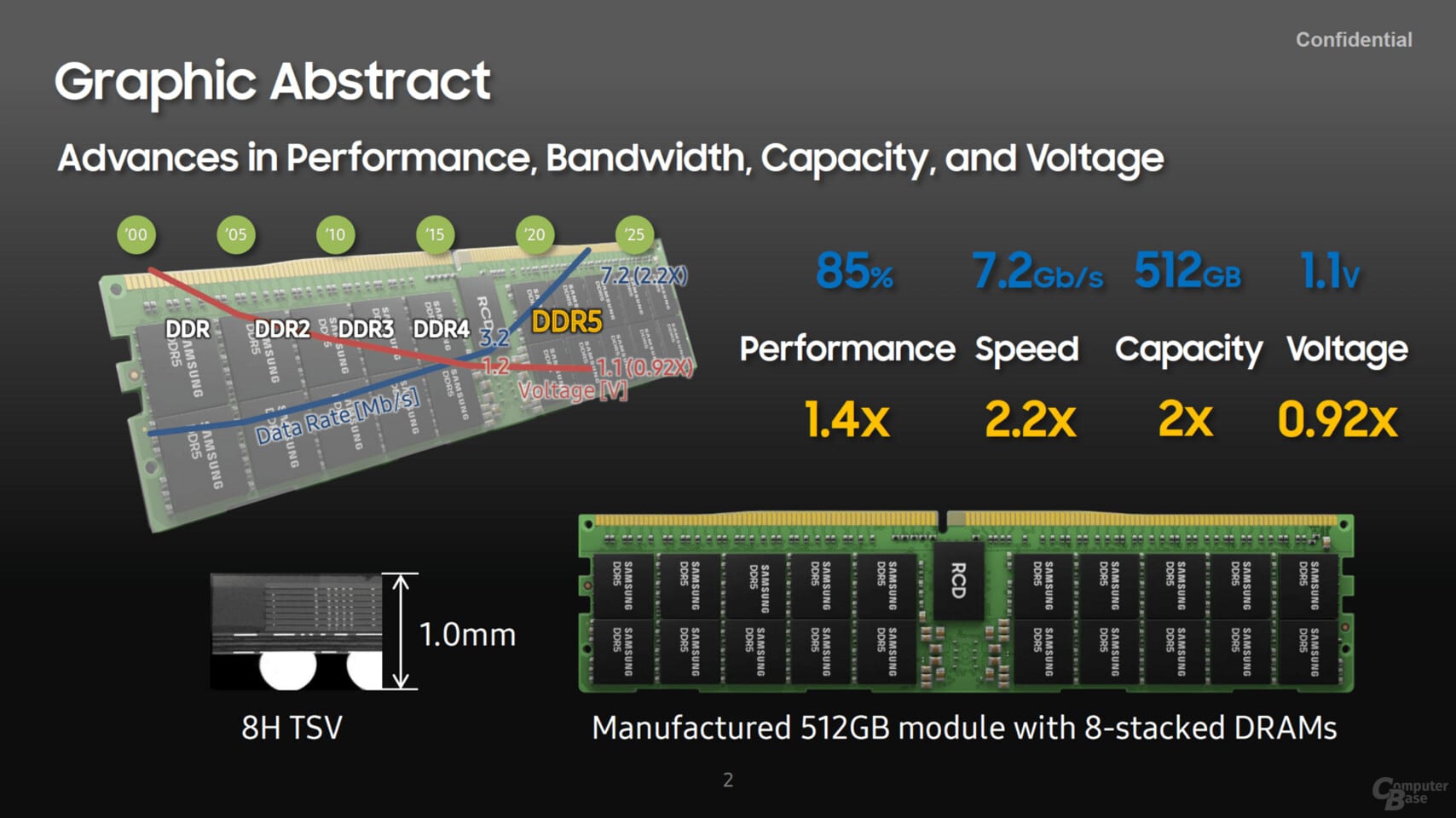

Samsung détaille son module mémoire DDR5-7200 de 512 Go

De la DDR5 TSV 8H haute de seulement 1 mm, alors que la DDR4 TSV 4H mesure 1,2 mm.

La mémoire X-NAND, qui combine le meilleur de la SLC et de la QLC, est désormais brevetée

Elle couple la densité de la mémoire QLC à la vitesse de la mémoire SLC.

Xiaomi présente CyberDog, son chien-robot open source

Un robot bardé de capteurs capable de courir à une vitesse maximale de 3,2 m/s.

AMD Ryzen 3D V-Cache : 23 000 TSV de 17 µm

Des détails sur l’interconnexion entre ce cache 3D vertical et le CCD.

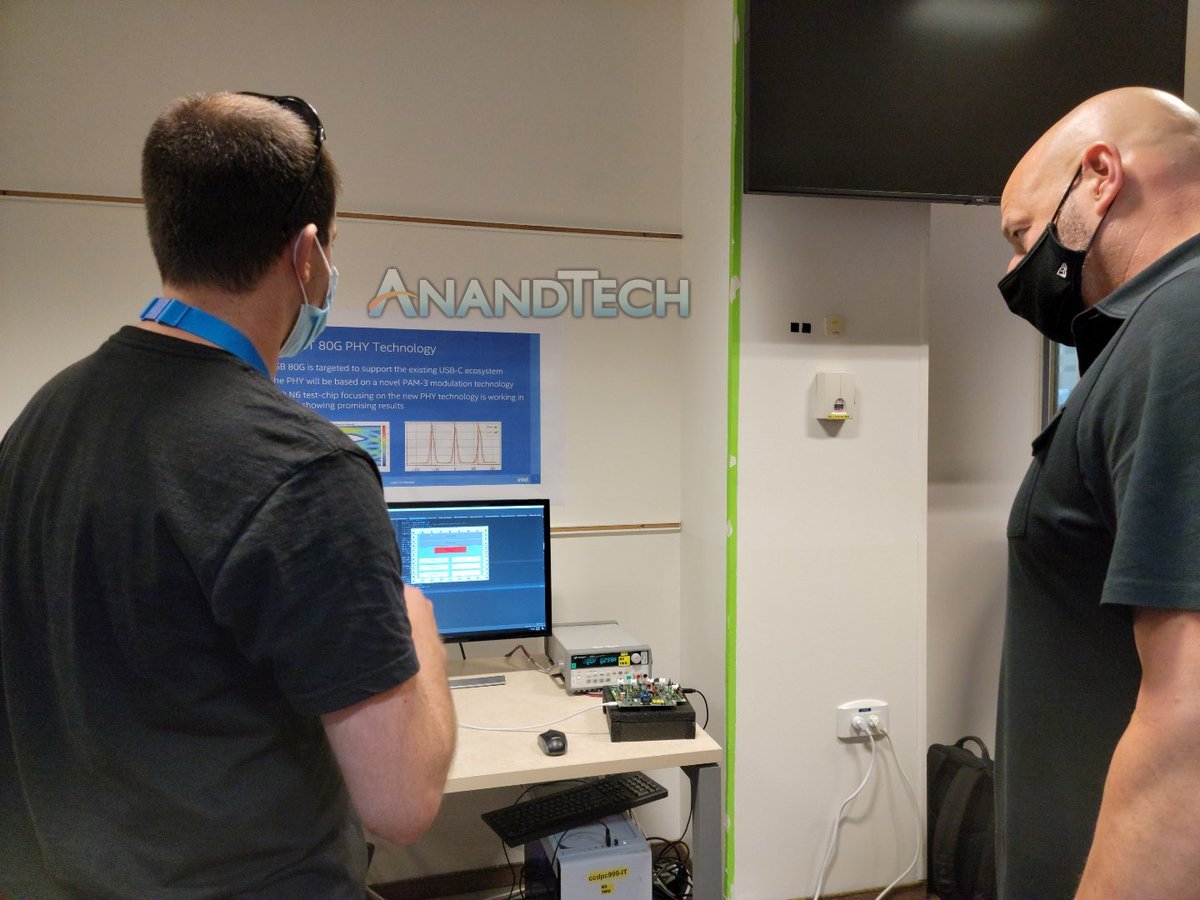

Le Thunderbolt 5 double le débit par rapport au Thunderbolt 4 : jusqu’à 80 Gbit/s

Pour y parvenir, Intel met en place une modulation PAM-3 qui transfère 3 bits sur 2 cycles.

Kioxia teste de la mémoire 3D NAND à 6 bits par cellule

Et mentionne aussi de la mémoire à 8 bits par cellule.

C’est officiel, Intel renomme ses nœuds de gravure : l’Enhanced SuperFin 10 nm devient l’Intel 7

Intel 7, Intel 4, Intel 3, Intel 20A puis Intel 18A : une feuille de route ambitieuse avec un nœud de gravure par an jusqu’en 2025.

NVIDIA présente le supercalculateur Cambridge-1, le plus puissant du Royaume-Uni

Un supercalculateur "conçu pour relever les défis médicaux les plus pressants grâce à l’IA".

Le 3 nm de Samsung repoussé à 2024 ?

Les transistors GAAFET de Samsung arriveraient un peu plus tard que prévu.