Pour y parvenir, Intel met en place une modulation PAM-3 qui transfère 3 bits sur 2 cycles.

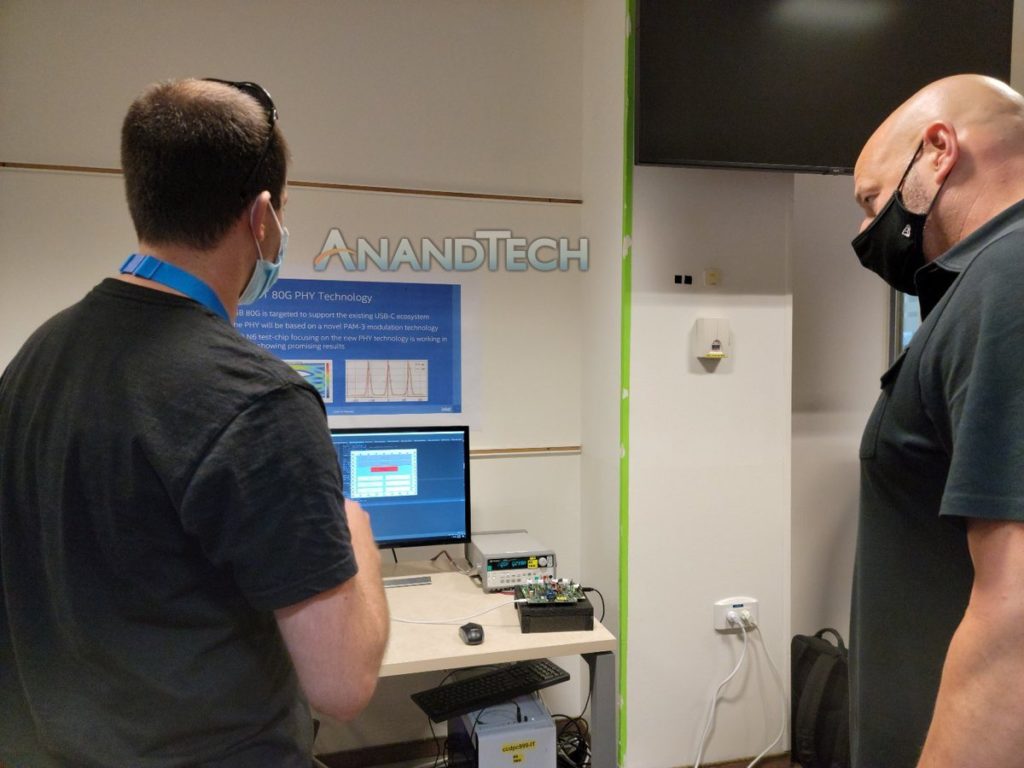

Gregory M Bryant, vice-président exécutif et directeur général du Client Computing Group d’Intel, a partagé sur Twitter quelques clichés de sa visite au sein des labos de l’entreprise situés en Israël. L’une des photographies, supprimée mais préalablement enregistrée par Anandtech, dévoile des informations sur l’interface Thunderbolt 5. En effet, sur l’affiche placardée au mur, on lit “80G PHY Technology”, que “l’USB 80G vise à soutenir l’écosystème USB-C existant” et qu’il utilise une modulation PAM-3 (modulation d’impulsion en amplitude, pulse amplitude modulation en anglais).

Ces deux inscriptions nous apprennent donc que le Thunderbolt 5 utilisera toujours un connecteur USB-C et que la bande passante atteindra 80 Gbit/s. Le Thunderbolt 5 offrira ainsi un débit doublé par rapport à celui des normes Thunderbolt 3 et Thunderbolt 4 (40 Gbit/s). Cela devrait notamment se traduire par la prise en charge de fréquences de rafraîchissement plus élevées qu’actuellement. Pour rappel, le Thunderbolt 4 permet du 4K/120 Hz ou du 8K/60 Hz.

C’est officiel, Intel renomme ses nœuds de gravure : l’Enhanced SuperFin 10 nm devient l’Intel 7

Des puces de test gravées en 6 nm par TSMC

À mi-chemin entre le NRZ (non-return-to-zero) et le PAM-4, le PAM-3 transfère 1,5 bits par cycle (contre 1 bit par cycle pour le NRZ et 2 bits par cycle pour le PAM-4). Pour expliquer brièvement les choses, les signaux NRZ sont binaires (0 et 1). Les signaux PAM-4 se basent quant à eux sur des formats à deux bits, c’est-à-dire des combinaisons de 0 et de 1 (00, 01…). Le PAM-3 utilise des états -1, 0 et +1. En pratique, cette méthode s’avèrerait plus efficace que la NRZ et plus facile à mettre en œuvre que la PAM-4.

| Type de modulation | Bits | Cycles | Bits par cycle |

| NRZ | 1 | 1 | 1 |

| PAM-3 | 3 | 2 | 1,5 |

| PAM-4 | 2 | 1 | 2 |

Enfin, la dernière ligne du poster stipule que “…la puce de test N6 axée sur la nouvelle technologie PHY fonctionne […] et donne des résultats prometteurs”. Le N6 désigne le le nœud de fabrication en 6 nm de TSMC. À l’évidence, Intel a donc recours à des puces de test fabriquées par TSMC.

Source : AnandTech