Ainsi que de la mémoire NAND 3D à huit plans / 210 couches capable d’atteindre un débit de 205 Mo/s. Les deux sociétés détailleront toutes leurs innovations dans quelques jours lors du Symposium on VLSI Technology and Circuits.

Le 11 juin prochain, dans le cadre du Symposium on VLSI Technology and Circuits, qui se déroulera du 11 au 16 juin à Kyoto (Japon), Kioxia et Western Digital présenteront leurs dernières innovations en matière de dispositifs mémoire NAND 3D. Le programme détaille déjà une bonne partie d’entre elles.

Kioxia présentera notamment un dispositifs 3D NAND à 8 plans ainsi que des circuits 3D NAND à plus de 300 couches. Il sera également question d’une technique de gravure pour de la 3D NAND à 400 couches.

À lire > Kioxia dévoile les premiers dispositifs UFS utilisant l’interface MIPI M-PHY v5.0

Jusqu’à 205 Mo/s pour la NAND 3D à huit plans

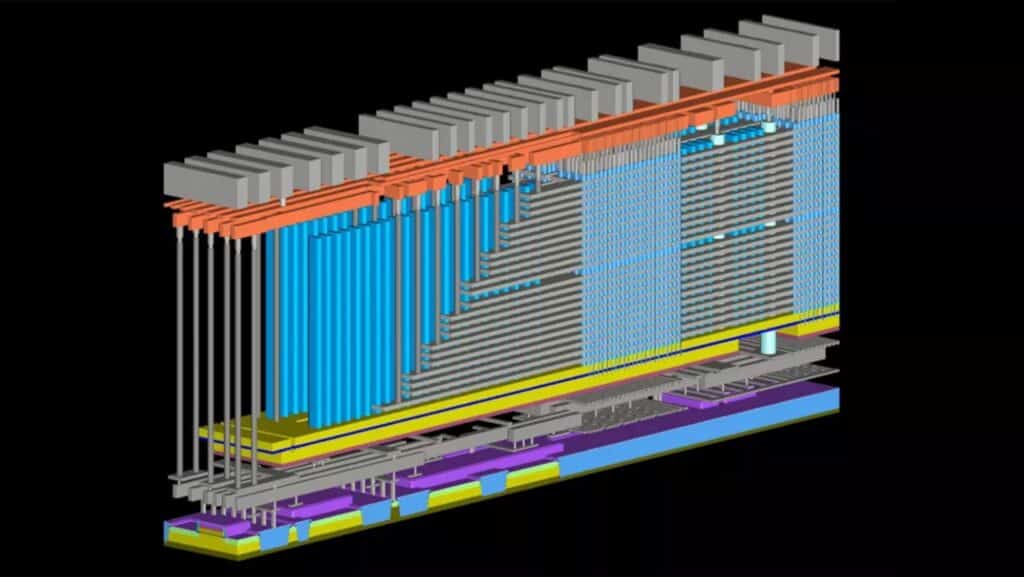

Afin d’augmenter les performances de la mémoire, l’une des approches consiste à augmenter le nombre de plans, au prix d’une complexité accrue. Kioxia prévoit des dispositifs NAND TLC 3D de 1 Tbit à huit plans avec 210 couches actives et une interface offrant un débit de 3,2 GT/s. C’est a priori une version retravaillée de la mémoire flash 3D NAND à 218 couches présentée fin mars, laquelle comporte quatre plans. Ce dispositif à huit plans stocke trois bits par cellule de mémoire et atteint une densité de 17 Gbit par millimètre carré. Il offre une latence de lecture de 40 microsecondes et un débit de programmation de 205 Mo/s. Ces caractéristiques sont rendues possibles par une technique dite de « one-pulse-two-strobe » qui détecte deux cellules mémoire par impulsion. En outre, pour éviter une congestion du câblage, Kioxia utilise des décodeurs d’adresse de rangée hybrides (X-DEC).

A lire aussi, les dernières actualités en matière de stockage :

- Stockage SSD : performances, disponibilité, quel modèle acheter au meilleur prix en 2025 ?

- Samsung 990 EVO Plus : la nouvelle arme fatale des créateurs de contenus et des gamers

- SanDisk conçoit la plus grande carte mémoire SD jamais créée, d’une capacité de 8 To

- Meilleure carte microSD : quel modèle de carte mémoire choisir en 2024 ?

NAND 3D à plus de 300 et 400 couches

Outre les dispositifs 3D NAND à huit plans, Kioxia et Western Digital collaborent également au développement de dispositifs 3D NAND comportant plus de 300 couches. Selon le document T7-1, les deux entreprises ont mis au point des techniques de cristallisation latérale induite par le métal (MILC) expérimentales afin de modeler des canaux de silicium monocristallins de 14 microns de long qui, associés à une méthode de surfaçage au nickel destinée à éliminer les impuretés et les défauts du silicium, améliorent les performances de la matrice de cellules. À la clef, un bruit de lecture réduit d’au moins 40 % et une conductance multipliée par dix.

Enfin, concernant la NAND 3D à plus de 400 couches, il est question d’un nouveau procédé de gravure pour le modelage élaboré par Tokyo Electron. Cette méthode permet de percer rapidement des canaux verticaux de plus de 10 microns (10 μm) pour des nœuds NAND 3D à 400 couches. Les auteurs d’un article T3-2 évoquent une gravure à travers un wafer à une profondeur de 10 microns en 33 minutes environ, le tout avec une réduction de l’empreinte carbone de l’ordre de 84 % par rapport à d’autres procédés de gravure.

Source : eeNewseurope via Tom’s Hardware US