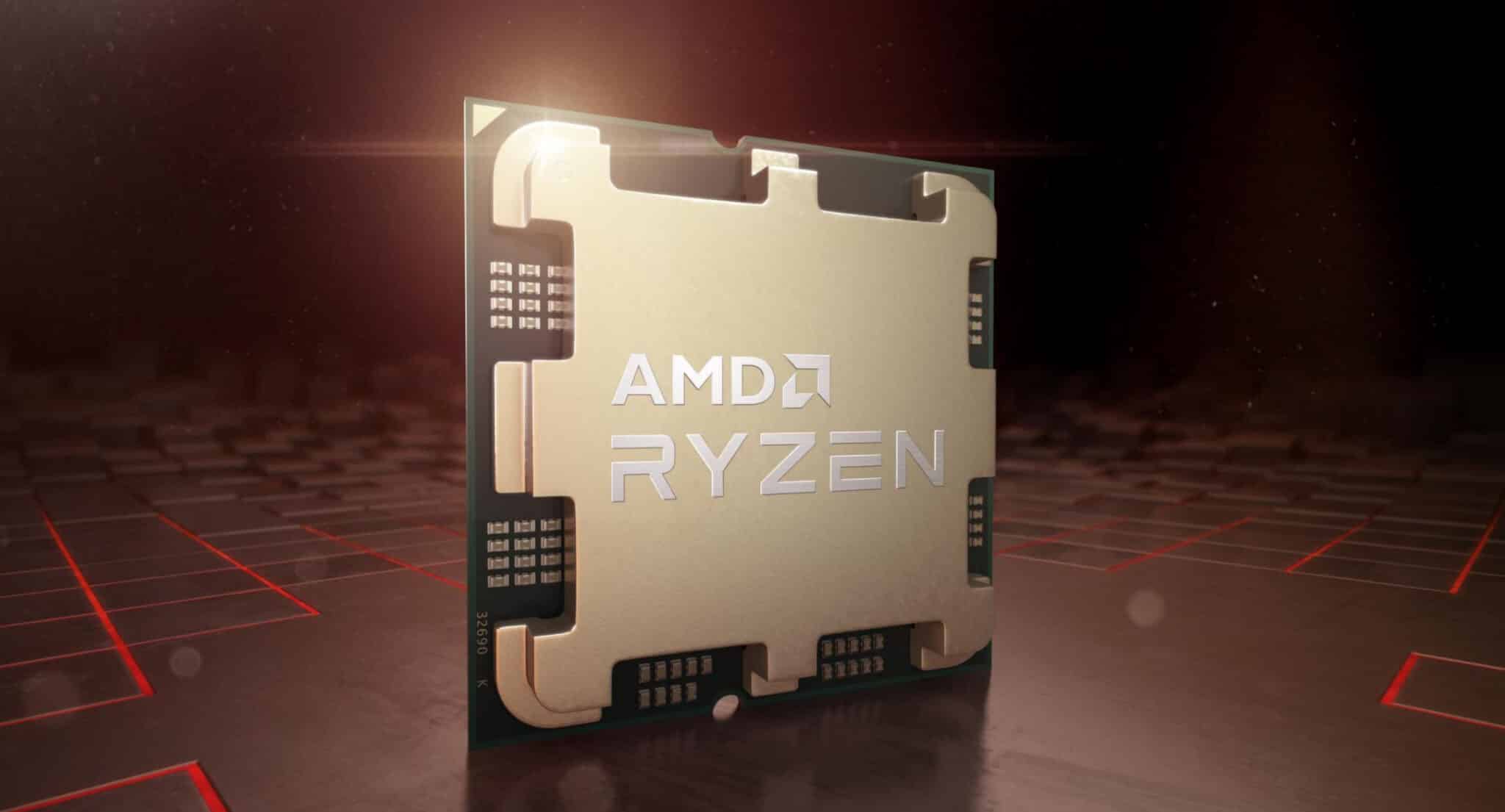

Test MSI Raider GE78 : un notebook gaming monstrueusement puissant, mais bruyant

MSI a dévoilé en début d'année son nouveau Raider GE78HX 14V, un notebook gaming basé sur un Core de 14ème génération et une GeForce RTX 40 Series. La version qui nous intéresse ce jour se…

![predatorx45 2[1]](https://www.tomshardware.fr/content/uploads/sites/3/2023/09/predatorx45-21-240x170.jpg)